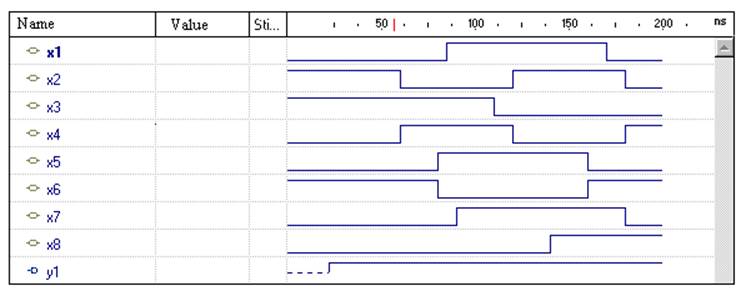

Временная диаграмма работы логического элемента К155ЛА2 с временем задержки tз=22 нс. Приведена на рис.2

Рис.2. Временная диаграмма работы логического элемента К155ЛА2

2.2 Логический элемент К155ЛА3

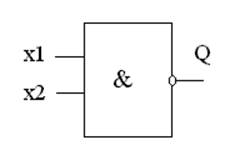

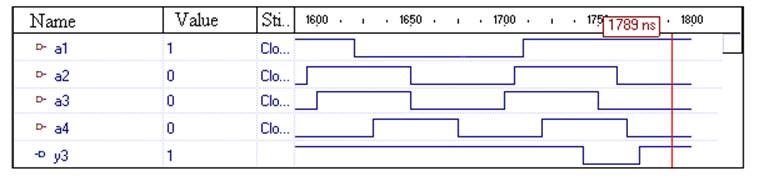

Логический элемент серии ТТЛ К155ЛА3 выполняет логическую функцию 2и-не.

Схема электрическая принципиальная приведена на рис.3.

Рис.3. Схема электрическая принципиальная К155ЛА3

Логическая функция элемента:

![]()

Табл.2. Таблица истинности элемента 2и-не

|

X1 |

X2 |

Q |

|

0 |

0 |

1 |

|

0 |

1 |

1 |

|

1 |

0 |

1 |

|

1 |

1 |

0 |

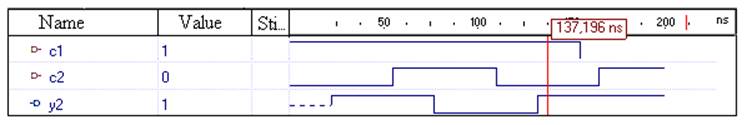

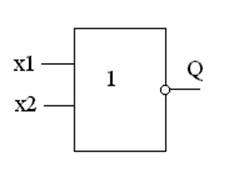

Временная диаграмма работы логического элемента К155ЛА3 с временем задержки tз=22 нс. Приведена на рис. 4.

Рис. 4. Временная диаграмма работы логического элемента К155ЛА3

2.3 Логический элемент К155ЛА6

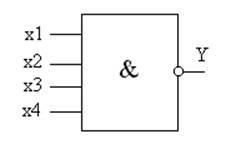

Логический элемент серии ТТЛ К155ЛА6 выполняет логическую функцию 4и-не.

Схема электрическая принципиальная приведена на рис.5.

Рис.5 Схема электрическая принципиальная К155ЛА6

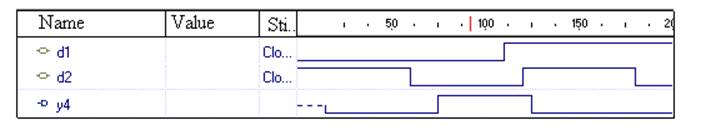

Логическая функция элемента:

Табл. 3. Таблица истинности элемента 4и-не.

|

X1 |

X2 |

X3 |

X4 |

Y |

|

0 |

0 |

0 |

0 |

1 |

|

0 |

0 |

0 |

1 |

1 |

|

0 |

0 |

1 |

0 |

1 |

|

… |

… |

… |

… |

1 |

|

1 |

1 |

1 |

0 |

1 |

|

1 |

1 |

1 |

1 |

0 |

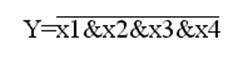

Временная диаграмма работы логического элемента К155ЛА6 с временем задержки tз=22 нс приведена на рис.6.

Рис.6. Временная диаграмма работы логического элемента К155ЛА6.

2.4. Логический элемент К155ЛЕ1

Логический элемент серии ТТЛ К155ЛЕ1 выполняет логическую функцию

2или-не.

Схема электрическая принципиальная приведена на рис.7.

Рис.7 Схема электрическая принципиальная К155ЛЕ1

Логическая функция элемента:

![]()

Табл.4. Таблица истинности элемента 2или-не

|

X1 |

X2 |

Q |

|

0 |

0 |

1 |

|

0 |

1 |

0 |

|

1 |

0 |

0 |

|

1 |

1 |

0 |

Временная диаграмма работы логического элемента К155ЛЕ1 с временем задержки tз=15 нс приведена на рис.8.

Рис.8. Временная диаграмма работы логического элемента К155ЛЕ1

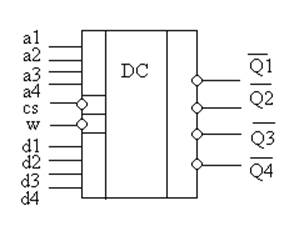

2.5. Схема ОЗУ

Микросхема К155РУ2 - высокоскоростное ОЗУ с ёмкостью 64 бит. Данные в ОЗУ можно записывать и считывать. При считывании информации из ОЗУ она не разрушается . Ячейки в памяти организованы в матрицу, имеющую 16 рядов и 4 колонки, что соответствует логической организации 16 слов по 4 бита каждое.

Схема К155РУ2 приведена на рис.9.

Рис.9. Схема электрическая принципиальная микросхемы К155РУ2.

Логика работы микросхемы показана в таблице 5

Табл.5. Состояние ОЗУ К155РУ2.

|

Режим работы |

Вход |

Выход Qn |

||

|

cs |

w |

dn |

||

|

запись |

0 0 |

0 0 |

0 1 |

1 0 |

|

считывание |

0 |

1 |

x |

dn |

|

Запрет записи |

1 1 |

0 0 |

0 1 |

1 0 |

|

Отключение выходов |

1 |

1 |

x |

1 |

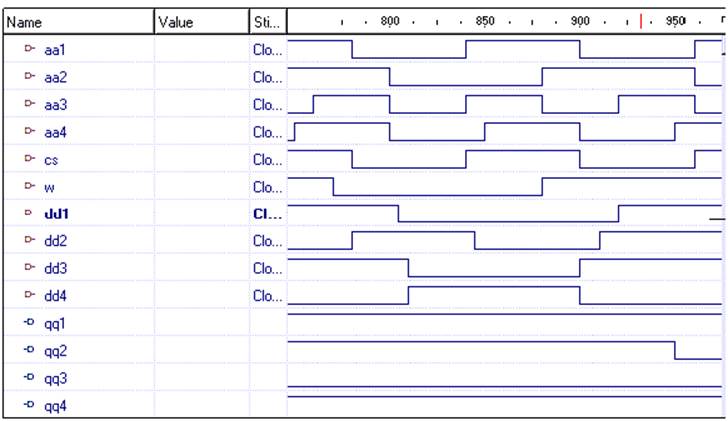

Временная диаграмма работы микросхемы К155РУ2 показана на рис.10.

Рис.10. Временная диаграмма работы микросхемы К155РУ2

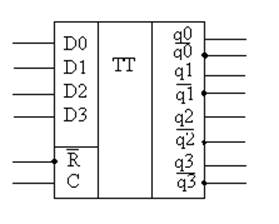

2.6. Схема D-триггера К155ТМ8

Схема D-триггера К155ТМ8 электрическая принципиальная приведена на рис.11.

Рис.11. Схема D-триггера К155ТМ8

Микросхема К155ТМ8 серии ТТЛ содержит четыре D-триггера с общими входами синхронного сброса R и тактового запуска С.Логика работы микросхемы показана в таблице 6.

Табл.6. Состояния триггера микросхемы К155ТМ8.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.