способу хранения информации

различают триггеры с активным хранением информации (выходной информационный

сигнал действует постоянно); с пассивным хранением информации (выходной

информационный сигнал может быть получен только с помощью специального опорного

сигнала).Рассмотрим две базовые модели триггеров.

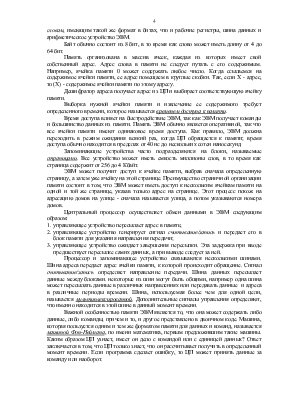

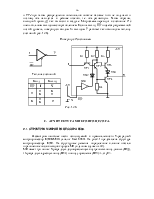

RS-триггер.

Схема RS-триггера, таблица состояний и временные диаграммы представлены на рис.

1.15.

Значения Qi и Qi+1

означают состояние выхода триггера Q до и

после подачи сигналов на входы R и S.

Система имеет два входа:

·

S - подача “1” на который вызывает

появление “1” на выходе Q ( в триггер

записывается “1”).

·

R - подача “1” на который приводит к

появлению “0” на выходе Q (т.е. в триггер

записывается “0”). Выход  во всех

случаях инвертирует состояние Q.

во всех

случаях инвертирует состояние Q.

При отсутствии сигналов и на R

и на S триггер сохраняет

состояние последней комбинации сигналов на входах R и S. Недостатком для

данного типа триггеров является наличие запрещенной комбинации сигналов, т.е.

одновременная подача “1” на входы R и S. В этом случае сигнал может принять любое

случайное состояние. Эти недостатки преодолены в дальнейших модификациях

триггеров - RSC, RST и других. Эти триггеры

являются одноступенчатыми, т.е. содержащими только одну триггерную ячейку,

состояние которой является практически одномоментной комбинацией входных

сигналов. Это заставляет предъявлять высокие требования к качеству сигналов.

Избежать этого позволяют двухступенчатые триггеры, в которых во входной

логическо-триггерной части состояния выходных сигналов формируются по мере

прихода входных сигналов, но передаются на выход, во вспомогательный триггер

памяти только в момент окончания входных воздействий (по заднему фронту

сигнала), так, что промежуточные состояния не фиксируются. Это так называемые JK- триггеры.

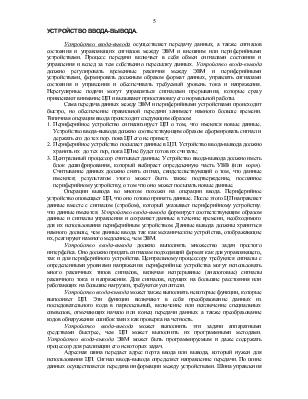

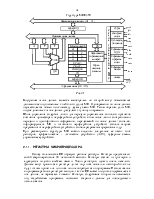

JK-триггеры.

Схема RS-триггера,

таблица состояний и временные диаграммы представлены на рис. 1.16.

Отличием данного типа триггера от

предыдущего является наличие дополнительного входа синхронизации С, который

может также выполнять функции счетного входа Т, если на входы J

и K. Следует

отметить еще два дополнительных свойства:

1. его выход принимает новое состояние с концом управляющего импульса,

т.е. JK-триггер срабатывает от заднего фронта

потенциального сигнала;

2. состояние J=K=1не является запрещенным, при

нем происходит (с окончанием входного сигнала) изменение состояния триггера на

противоположное, т.е. объединение входов J и

K образуют счетный вход.

В остальном можно считать, что J-вход

повторяет функции S-входа, а K-вход – функции R-входа . Кроме того, в схемах JK-триггеров

часто предусматривают и прямые R и S

входы от второго триггера, что делает его универсальным.

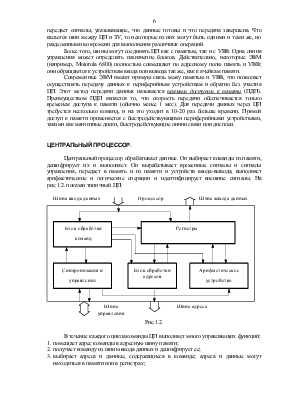

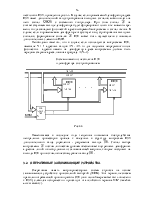

Параллельный

регистр.

Это регистр с

параллельным приемом и выдачей информации и служащий для ее хранения, который

можно также назвать регистром памяти.

Рассмотрим схему

параллельного регистра емкостью 3 бита, представленную на рис.1.17.

Регистр,

предварительно очищенный от записанной ранее информации импульсом, поданным на

вход сброса R, готов к записи трех бит информации в

виде кодовой комбинации на входах X1,X2,X3. При

кратковременном появлении “1” на входе C1,

разрешающем запись, триггеры, на вход S поступили “0”

, остаются в исходном состоянии ( на выходе записан “0”), а

триггеры, на вход которых поступили “1” , опрокидываются, так, что на их

выходах появится “1”, что соответствует кодовой комбинации, имевшейся на

входах X1,X2,X3. Очевидно, что после снятия “1” с

входа C1, записанная в триггерах комбинация будет

сохраняться независимо от последующих изменений на информационных входах.

Хранимую информацию можно воспроизвести на выходах Y1, Y2, Y3 подав “1” на вход считывания C2.

Запись и считывание кодовой комбинации в такой схеме идут одновременно,

параллельно для всех разрядов кодовой комбинации, поэтому регистр называется

параллельным.

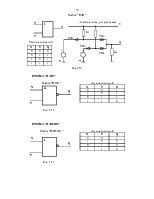

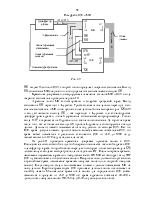

Последовательный

регистр.

Последовательный регистр или регистр сдвига в отличие от параллельного

предназначается для регистрации и хранения поступающей последовательно во

времени кодовой комбинации бинарных сигналов, причем продвижение ее элементов

по цепочке триггерных ячеек регистра (разрядов) и вывод на единственный выход

осуществляется пошагово, синхронно с приходом тактовых импульсов (рис. 1.18).

Пусть в сдвиговый регистр на JK-триггерах записывается комбинация “101”. Тогда по первому

тактовому импульсу триггер DD1 под воздействием “1”

на выходе J опрокинется и на его выходе Q1 появится “1”. Следующий триггер эта “1” не опрокинет,

так как в JK-триггерах запись происходит с концом

входных импульсов, а тактовый импульс уже исчез. В момент второго тактового

импульса “1” из триггера DD1 сдвинется

![]() во всех

случаях инвертирует состояние Q.

во всех

случаях инвертирует состояние Q.