указанным причинам целесообразнее реализовать RS триггеры на элементах И-НЕ.

Преобразованная логическая схема с учётом выбранной элементной базы

12. Разработка принципиальной схемы устройства

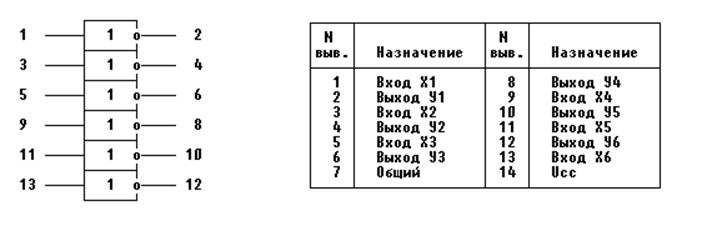

При проектировании устройства выберем следующие ИС:

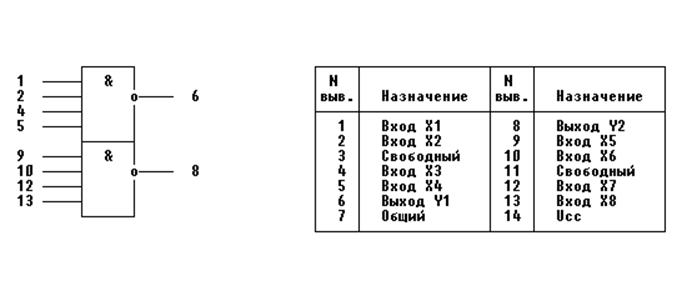

КР1533ЛА1 (2 элемента 4И-НЕ)

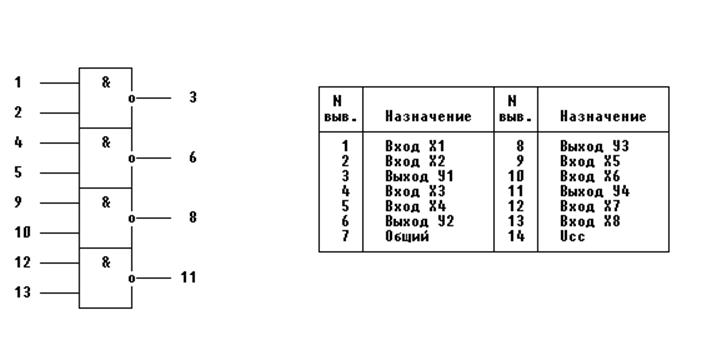

КР1533ЛА3 (4 элемента 2И-НЕ)

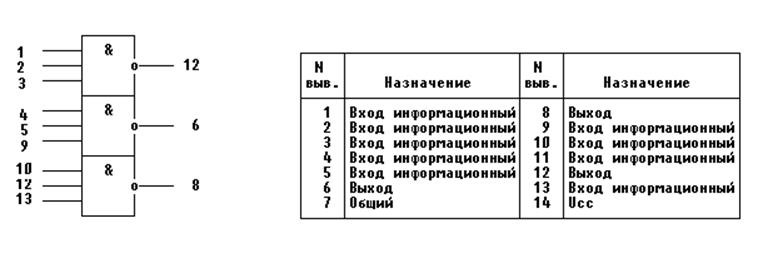

КР1533ЛА4 (3 элемента 3И-НЕ)

КР1533ЛН1 (6 инверторов)

|

№ |

Тип лэ |

количество лэ |

Тип ИС |

кол-во ИС |

число неиспользуемых лэ |

объем оборудования |

|

1 |

2И-НЕ |

14 |

КР1533ЛА3 |

4 |

2 |

10 |

|

2 |

3И-НЕ |

11 |

КР1533ЛА4 |

4 |

1 |

|

|

3 |

4И-НЕ |

2 |

КР1533ЛА1 |

1 |

- |

|

|

4 |

НЕ |

5 |

КР1533ЛН1 |

1 |

1 |

Питание подается на 14-ый вывод, а земля – на 7-ой вывод.

Чтобы исключить низкочастотные помехи, на печатных платах вблизи разъема устанавливают развязывающие конденсаторы. Для ТТЛ ИС их емкость обычно выбирается из расчета не менее 0.1 мкФ на одну ИС.

Для исключения ВЧ помех, развязывающие конденсаторы рекомендуется размещать по площади печатной платы из расчета один конденсатор на группу не более чем из 10 ИС. Для ТТЛ ИС их емкость обычно выбирается из расчета не менее 0.002 мкФ на одну ИС.

Выберем для установки на плате два конденсатора типа КМ-6-Н90-1.0мкФ и один конденсатор типа КМ-6-Н50-0.1мкФ.

Необходимо также преобразовать синтезированную схему с учетом выбранных способов обеспечения ее контролепригодности. Как видно из таблицы, для вывода контрольных точек на внешние узлы схемы могут использоваться четыре логических элемента, что позволяет обеспечить наблюдаемость состояния всех элементов памяти.

Таким образом, принципиальная схема устройства будет выглядеть следующим образом:

13. Расчет основных параметров устройства (время переключения, потребляемая мощность, время наработки на отказ)

|

Обозначение микросхемы |

Функциональное назначение |

Число выводов корпуса |

|

|

Кол-во |

|

КР1533ЛА3 |

4 лог. эл-та 2И-НЕ |

14 |

7 |

11 |

4 |

|

КР1533ЛА4 |

3 лог. эл-та 3И-НЕ |

14 |

10 |

11 |

4 |

|

КР1533ЛА1 |

2 лог. эл-та 4И-НЕ |

14 |

5 |

11 |

1 |

|

КР1533ЛН1 |

6 лог. эл-тов НЕ |

14 |

12 |

11 |

1 |

Рассчитаем время переключения синтезированного конечного автомата. Для оценки быстродействия синтезированного автомата необходимо определить наиболее длинный путь распространения сигналов в схеме при изменении входных сигналов.

Наиболее длинным будет путь:

НЕ→НЕ→2И-НЕ→4И-НЕ →Тр1(2И-НЕ→3И-НЕ)→3И-НЕ→3И-НЕ

Таким образом, время задержки составляет:

tз = 11+11+11+11+11+11+11+11=88 нс.

Полученное время подтверждает выполнение требований по быстродействию устройства, поскольку определенное в п.10 время его переключения составляет 89,3 нс.

Максимальная потребляемая схемой мощность определяется исходя из характеристик ИС и вариантов их коммутации. Вычислим потребляемую схемой мощность как сумму произведений потребляемых микросхемами мощностей на количество микросхем:

Интенсивность отказов устройства, содержащего разнотипные элементы, определяется следующим соотношением:

Среднее время наработки на отказ устройства составляет:

Tср = 1/λ

Перечень комплектующих элементов устройства и значений интенсивности их отказов

|

№ |

Тип элемента |

Число элементов Q |

λ [1/час] |

Q*λ [1/час] |

|

1 |

КР1533ЛА3 КР1533ЛА4 КР1533ЛА1 КР1533ЛН1 |

4 4 1 1 |

0.017*10-6 0.017*10-6 0.017*10-6 0.017*10-6 |

0.068*10-6 0.068*10-6 0.017*10-6 0,017*10-6 |

|

2 |

Паяные соединения |

152 |

10-9 |

0.152*10-6 |

|

3 |

Конденсаторы |

3 |

0.004*10-6 |

0.012*10-6 |

|

4 |

Вилка разъема |

1 |

0.011*10-6 |

0.011*10-6 |

|

Суммарная интенсивность отказов |

0.345*10-6 |

|||

Время наработки на отказ разработанного устройства при этом составит:

Тотк=106/0.345 = 2898550 час,

что удовлетворяет предъявленным требованиям по времени наработки на отказ.

14. Моделирование работы устройства,

анализ правильности функционирования

Проектируемое устройство представляет собой достаточно тривиальный автомат с памятью, имеющий всего шесть состояний. Это делает целесообразным применение методов тестового диагностирования, используя в качестве теста наборы значений входных переменных, обеспечивающие реализацию временной диаграммы работы устройства. Ниже приведена временная диаграмма работы синтезируемого устройства с отмеченными позициями отсчетов, по которым формируется проверяющий тест. Данный тест позволяет проверить правильность работы автомата при всех возможных сочетаниях моментов фронта и спада информационного импульса относительно тактового при различной длительности информационных импульсов.

Формирование проверяющего теста проектируемого конечного автомата

В результате получаем следующий массив входных сигналов:

Массив входных сигналов проверяющего теста

|

№ |

x2 |

x1 |

y |

№ |

x2 |

x1 |

y |

№ |

x2 |

x1 |

y |

№ |

x2 |

x1 |

y |

|

0 |

0 |

0 |

0 |

11 |

0 |

0 |

1 |

22 |

0 |

1 |

0 |

33 |

0 |

0 |

0 |

|

1 |

1 |

0 |

0 |

12 |

1 |

0 |

0 |

23 |

0 |

0 |

0 |

34 |

1 |

0 |

0 |

|

2 |

1 |

1 |

0 |

13 |

0 |

0 |

0 |

24 |

1 |

0 |

0 |

35 |

0 |

0 |

0 |

|

3 |

0 |

1 |

1 |

14 |

0 |

1 |

0 |

25 |

0 |

0 |

1 |

36 |

0 |

1 |

0 |

|

4 |

1 |

1 |

1 |

15 |

1 |

1 |

0 |

26 |

1 |

0 |

0 |

37 |

1 |

1 |

0 |

|

5 |

0 |

1 |

0 |

16 |

0 |

1 |

1 |

27 |

0 |

0 |

0 |

38 |

0 |

1 |

1 |

|

6 |

1 |

1 |

0 |

17 |

1 |

1 |

1 |

28 |

1 |

0 |

0 |

39 |

1 |

1 |

1 |

|

7 |

0 |

0 |

0 |

18 |

0 |

1 |

0 |

29 |

1 |

1 |

0 |

40 |

1 |

0 |

1 |

|

8 |

1 |

0 |

0 |

19 |

1 |

1 |

0 |

30 |

0 |

1 |

1 |

41 |

0 |

0 |

0 |

|

9 |

1 |

1 |

0 |

20 |

1 |

0 |

0 |

31 |

1 |

1 |

1 |

||||

|

10 |

1 |

0 |

0 |

21 |

0 |

0 |

0 |

32 |

1 |

0 |

1 |

Для обеспечения полноты теста, то есть возможности выявить

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.