БАЛТИЙСКИЙ ГОСУДАРСТВЕННЫЙ ТЕХНИЧЕСКИЙ УНИВЕРСИТЕТ «ВОЕНМЕХ» им. Д. Ф. УСТИНОВА

Кафедра ______

КУРСОВАЯ РАБОТА

по

учебной дисциплине _____________________________________________

на тему ___________________________________________________________

__________________________________________________________________

студента __________________________________________________________

Фамилия, Имя, Отчество студента группы ________________

ПРЕПОДАВАТЕЛЬ

____________ /____________________/

Подпись Фамилия

“____” _____________ 200__ г.

Санкт-Петербург

2008 г.

ТЕХНИЧЕСКОЕ ЗАДАНИЕ. 3

ПОЯСНИТЕЛЬНАЯ ЗАПИСКА.. 4

1. Анализ технического задания. 4

2. Составление логических уравнений устройства и их минимизация. 5

3. Разработка принципиальной схемы синтезируемого устройства. 6

4. Обоснование выбора элементной базы. 8

5. Расчет технических показателей устройства. 9

6. Моделирование работы устройства, анализ правильности функционирования и состязаний в схеме. 10

7. Разработка конструкции печатной платы. 12

8. Оценка степени выполнения задания. 13

СПИСОК ИСПОЛЬЗОВАННОЙ ЛИТЕРАТУРЫ.. 15

В соответствии с техническим заданием (ТЗ) для разработки преобразователя простого 4-х разрядного кода букв десятичного алфавита (0, 1, 2,…,9) в код по индивидуальному заданию (1, 5, 7, 11, 10, 13, 4, 2, 15, 3) с формирование бита паритета, была составлена таблица истинности (таблица 1) вида:

Таблица 1.

|

№ |

Вход |

Выход |

|||||||

|

|

|

|

|

|

|

|

|

|

|

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

|

1 |

0 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

|

2 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

0 |

|

3 |

0 |

0 |

1 |

1 |

1 |

0 |

1 |

1 |

0 |

|

4 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

|

5 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

1 |

0 |

|

6 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

|

7 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

0 |

|

8 |

1 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

|

9 |

1 |

0 |

0 |

1 |

0 |

0 |

1 |

1 |

1 |

|

10 |

1 |

0 |

1 |

0 |

x |

x |

x |

x |

x |

|

11 |

1 |

0 |

1 |

1 |

x |

x |

x |

x |

x |

|

12 |

1 |

1 |

0 |

0 |

x |

x |

x |

x |

x |

|

13 |

1 |

1 |

0 |

1 |

x |

x |

x |

x |

x |

|

14 |

1 |

1 |

1 |

0 |

x |

x |

x |

x |

x |

|

15 |

1 |

1 |

1 |

1 |

x |

x |

x |

x |

x |

Бит паритета, в соответствии с ТЗ выбран четным. Например, если по выходам Y получаем 1010, это число содержит две «1», следовательно, бит паритета равен 1, а число 0010, одну 1 – бит паритета равен 0.

Для простоты составления логических уравнения и их минимизации были составлены карты Карно.

|

1 |

1 |

1 |

1 |

|

1 |

x |

x |

1 |

|

x |

x |

x |

x |

|

0 |

0 |

0 |

1 |

|

0 |

0 |

0 |

1 |

|

1 |

x |

x |

1 |

|

x |

x |

x |

x |

|

1 |

0 |

0 |

0 |

|

0 |

0 |

1 |

0 |

|

1 |

x |

x |

0 |

|

x |

x |

x |

x |

|

1 |

0 |

0 |

1 |

|

0 |

1 |

0 |

0 |

|

1 |

x |

x |

0 |

|

x |

x |

x |

x |

|

0 |

1 |

0 |

1 |

|

0 |

1 |

1 |

0 |

|

1 |

x |

x |

1 |

|

x |

x |

x |

x |

|

1 |

0 |

1 |

0 |

В результате минимизации были получены следующие выражения:

![]()

![]()

![]()

![]()

![]()

По полученным выражениям в программном пакете OrCad

9.2 были составлены две схемы (Рис. 1 и Рис. 2.):

Рис. 1. Принципиальная схема устройства. Вариант № 1.

Рис. 2. Принципиальная схема устройства. Вариант № 2.

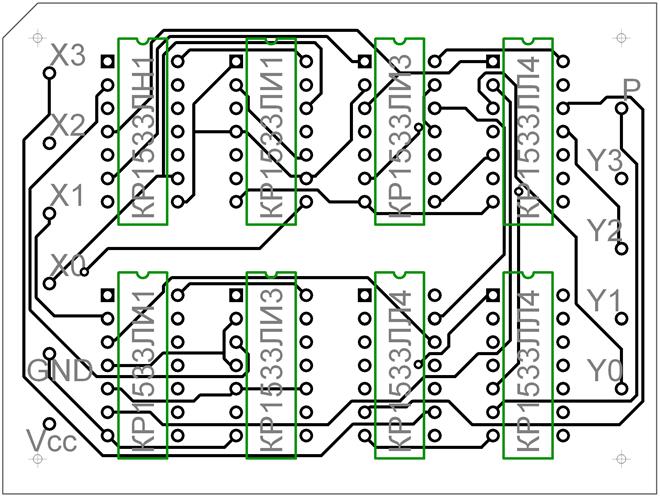

В принципиальной схеме устройства были использованы элементы серии 74ALSxxxx фирмы Texas Instruments. Отечественным аналогом данной серии являются маломощные быстродействующие интегральные микросхемы серии КР1533 предназначенные для организации высокоскоростного обмена и обработки информации, временного и электрического согласования сигналов в вычислительных системах. Микросхемы серии КР1533 по сравнению с извесными сериями логических ТТЛ микросхем обладают минимальным значением произведения быстродействия на рассеиваемую мощность.

Конструктивно микросхемы этой серии выполнены в 14-, 16-, 20- и 24- выводных стандартных пластмассовых корпусах типа 201.14-1, 238.16-1, 2140,20-8 и 2142.24-2.

Технические характеристики приведены в таблице 2.

Таблица 2.

|

Обозначение микросхемы |

Аналог |

Назначение |

|

|

Напряжение питания |

Рабочий диапазон температур |

Придельный диапазон температур |

|

КР1533ЛИ1 |

74ALS08 |

4 - 2И |

16 |

12 |

5В ±10% |

-10 - +70 |

-60 - +85 |

|

КР1533ЛИ3 |

74ALS11A |

3 - 3И |

12 |

11,5 |

5В ±10% |

-10 - +70 |

-60 - +85 |

|

КР1533ЛЛ4 |

74ALS32 |

4 - 2ИЛИ |

39 |

13 |

5В ±10% |

-10 - +70 |

-60 - +85 |

|

КР1533ЛН1 |

74ALS04B |

6 - НЕ |

12 |

9,5 |

5В ±10% |

-10 - +70 |

-60 - +85 |

Так как было предложено два варианта принципиальной схемы расчет производится для двух схем.

· Напряжение питания 5В ±10% для обеих схем.

· Потребляемая мощность всего устройства вычисляется сложением потребляемой мощности всех элементов. Для схемы № 1 Pср не превышает 185мВт. Для схемы №2 Pср не превышает 190мВт.

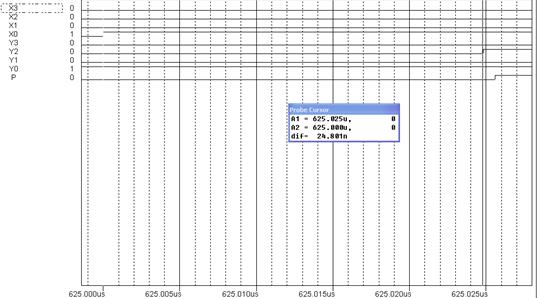

· Время формирования выходного сигнала определялось для двух схем экспериментально. Пример снятия показаний приведен на рис. 3. Полученные данные приведены в таблице 3:

Таблица 3.

|

Выход |

tз.ср, нс |

|

|

Схема № 1 |

Схема № 2 |

|

|

Y0 |

13.507 |

13 |

|

Y1 |

24.783 |

24.43 |

|

Y2 |

22.333 |

24.33 |

|

Y3 |

23.65 |

26.285 |

|

P |

21.836 |

22.634 |

· Как видно из таблицы 2 обе схемы имеют диапазон температур соответствующий ТЗ.

· Перегрузки до 500g.

· Одиночные удары с ускорением не более 150g длительностью 0,1-2 мс.

· Вибрация с частотой 1-2000 Гц и ускорением не более 20g.

Рис. 3. Снятие tз. на временной диаграмме. tз. для Y2 = 24,801нс

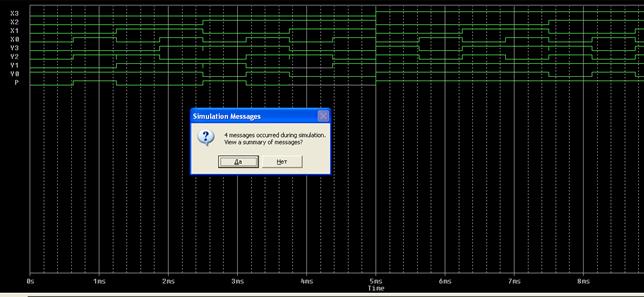

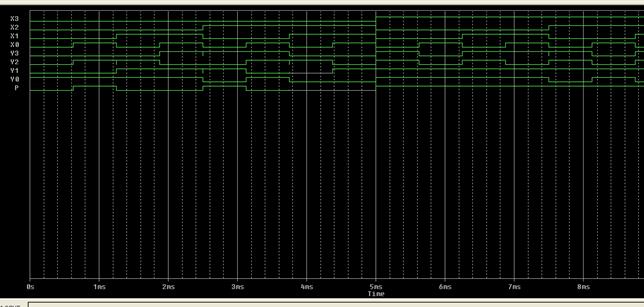

На рисунках 4 и 5 изображены временные диаграммы, полученные в ходе модулирования работы схем № 1 и № 2, соответственно в программном пакете OrCad 9.2.

Рис. 4. Временная диаграмма схемы № 1.

Рис. 5. Временная диаграмма схемы № 2.

Как видно из временной диаграммы обе схемы функционирую правильно.

Следует отметить, что в схеме № 1 было зафиксировано 4 состязания, а в схеме № 2 - 8 состязаний.

Во время анализа работы схемы № 1 было найдено решение для ее модернизации, заменить элементы 74ALS08 на элементы 74ALS11A и закоротить у них один вход. Принципиальная схема модернизированной схемы приведена на рис. 6. Модернизация привела к снижению потребляемой мощности со 185мВт до 177мВт, а так же к улучшению tз.ср. Сравнительные данные приведены в таблице 4

Таблица 4.

|

Выход |

tз.ср, нс |

|

|

Схема № 1 |

Схема № 1-б |

|

|

Y0 |

13.507 |

13 |

|

Y1 |

24.783 |

24,428 |

|

Y2 |

22.333 |

22,164 |

|

Y3 |

23.65 |

22,9 |

|

P |

21.836 |

21 |

Рис. 6. Принципиальная схема устройства. Вариант № 1-б.

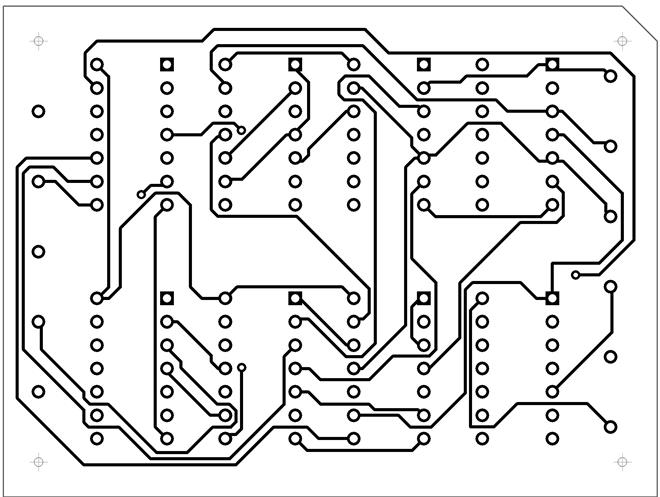

В соответствии с принципиальной схемой № 1 (рис. 1.) програмном пакете DipTrace была разработана 2-х сторонняя печатная плата. Верхняя сторона изображена на рис. 7, нижняя на рис. 8.

Рис. 7. Верхняя сторона печатной платы.

Рис. 8. Нижняя сторона платы.

Оценка степени выполнения задания приведена в таблице 5.

Таблица 5

|

Требование к устройству |

Соответствующая характеристика устройства |

||||

|

Схема № 1 |

Схема № 1-б |

Соответствие требованию |

Схема № 2 |

Соответствие требованию |

|

|

Напряжения питания 5±5% |

5±10% |

5±10% |

нет |

5±10% |

нет |

|

потребляемая мощность: не более 250 мВт |

185мВт |

177мВт |

да |

189 мВт |

да |

|

время формирования выходного сигнала не более 25 нс |

Y3: 23,65 нс Y2: 22,33 нс Y1: 24,783 нс Y0: 13,507 нс P: 21,836 нс |

Y3: 22,9 нс Y2: 22,164 нс Y1: 24,428 нс Y0: 13 нс P: 21 нс |

да |

Y3: 26,285 нс Y2: 24,33 нс Y1: 24,43 нс Y0: 13 нс P: 22,634 нс |

нет |

|

диапазон рабочих температур от минус 300С до плюс 400С |

от минус 100С до плюс 700С |

от минус 100С до плюс 700С |

нет |

от минус 100С до плюс 700С |

нет |

|

перегрузки до 5g |

перегрузки до 500g |

перегрузки до 500g |

да |

перегрузки до 500g |

да |

|

одиночные удары с ускорением не более 10g длительностью 0,1 – 1 мкс |

одиночные удары с ускорением не более 150g длительностью 0,1-2 мс |

одиночные удары с ускорением не более 150g длительностью 0,1-2 мс |

да |

одиночные удары с ускорением не более 150g длительностью 0,1-2 мс |

да |

|

вибрация с частотой 10 – 500 Гц и ускорением не более 10g |

вибрация с частотой 1-2000 Гц и ускорением не более 20g |

вибрация с частотой 1-2000 Гц и ускорением не более 20g |

да |

вибрация с частотой 1-2000 Гц и ускорением не более 20g |

да |

Несоответствие диапазона температур объясняется чувствительностью

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.