Вторая часть

таблицы 5.2 реализуется на втором мультиплексоре аналогично. Отличие будет

состоять в том, что на стобирующий вход ![]() второго

мультиплексора заводится не сама переменная

второго

мультиплексора заводится не сама переменная ![]() , а ее

инвертированное значение

, а ее

инвертированное значение ![]() . Из второй части

таблицы 5.2 по аналогии получаем значения сигналов на информационных входах

второго мультиплексора. Схема реализации сумматора по модулю 2 на четыре входа

приведена на рис. 5.2.

. Из второй части

таблицы 5.2 по аналогии получаем значения сигналов на информационных входах

второго мультиплексора. Схема реализации сумматора по модулю 2 на четыре входа

приведена на рис. 5.2.

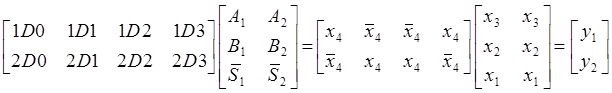

Реализованная

логическая функция ![]() , представленная в матричном

виде, может быть записана как:

, представленная в матричном

виде, может быть записана как:

(5.2)

![]()

ОПИСАНИЕ ЛАБОРАТОРНОГО СТЕНДА

Функциональные возможности модуля определяются его элементным составом, который включает:

1. Мультиплексор К155КП1 – 1 шт. (рис. 3.9 с).

2. Мультиплексор К155КП2 – 2 шт. (рис. 3.9 а).

3. Мультиплексор К155КП7 – 2 шт. (рис.3.9 в).

4. 4 – разрядный регистр К155ИР1 – 4 шт.

5. 8 – разрядный регистр К155ИР13 - 2 шт., а также вспомогательные логические элементы.

6. Инверторы – 6 шт. (элементы 5, 6, 7, 8, 9, 10)

7. Элементы задержки – 2 шт. (4, 11)

8. Элементы 2И - НЕ – 4 шт. (12, 13, 14, 15).

9. Элементы 3И – НЕ – 4 шт. (20, 21, 26, 27).

10.Элемент 4И – НЕ – 1 шт. (22).

11.Элемент 8И –НЕ – 1 шт. (23).

12.Элемент 2ИЛИ – 4 шт. (24, 25, 28, 29).

Для

формирования параллельного информационного кода на плате расположены 16

тумблеров- ![]() .

.

Для управления работой схем

преобразователей в составе модуля имеется пересчетная схема, включающая

генератор тактовых импульсов ![]() и двоичный СТ.

Коэффициент пересчета может изменяться с помощью тумблеров

и двоичный СТ.

Коэффициент пересчета может изменяться с помощью тумблеров ![]() .

.

Органы управления пересчетной схемой включают в себя:

- кнопку «ПУСК» для запуска схем преобразователя как в ручном, так и в автоматическом режимах;

- тумблер «Ручной» - «Авт.» для выбора режима запуска работы преобразователя;

- тумблер «1 Гц.» - «1 Кгц.» для выбора частоты генератора тактовых импульсов;

- тумблер «Цикл.» - «Спор.» для выбора режима работы преобразователя.

Для индикации сформированного последовательного кода в составе модуля имеется 16-разрядный «Регистр индикации», имеющий отдельные входы синхронизации и обнуления.

ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ

1. Ознакомиться с краткими сведениями из теории к лабораторной работе.

2. Получить у преподавателя техническое задание.

3. По таблице истинности составить матрицы входных переменных, адресации и выходных переменных.

4. На основании п.3 составить принципиальную схему реализации.

5. Реализовать принципиальную схему.

6. Пересчетную схему с требуемым коэффициентом пересчета перевести в режим запуска «РУЧНОЙ» и режим работы «СПОР.». Частоту генератора тактовых импульсов установить «1 Гц.».

7. Включить питание лабораторного стенда.

8. Кнопкой «СБОРС» установить «Регистр индикации» в нулевое состояние.

9. Выход синхронизированной схемы завести на вход «Регистра индикации».

10. Проверить работу схемы.

1. Техническое задание.

2. Таблица истинности.

3. Матрицы входных переменных, адресации и выходных переменных.

4. Принципиальные схемы реализации.

5. Выводыю

1. Схема контроля кода на четность для 3-разрядного кода.

2. Схема контроля кода на нечетность для 4-разрядного кода.

3. Мажоритарный логический элемент на 5 входов.

4. Сумматор по модулю 2 на 5 входов.

5. Схема сравнения двух 2-разрядных кодов на равенство.

6.

Схема сравнения двух 4-разрядных

кодов на неравенство ![]() .

.

7.

Пороговое устройство четырех

входных переменных с порогом ![]() . Устройство обеспечивает

индикацию состояний, при которых уровень логической «1» возникает на двух, трех

или четырех входах одновременно.

. Устройство обеспечивает

индикацию состояний, при которых уровень логической «1» возникает на двух, трех

или четырех входах одновременно.

8. Узел защиты дешифратора, имеющего 4 выхода. Узел обеспечивает выявление комбинаций на выходе дешифратора, которые содержат больше одной «1».

Зельдин Е. А. Цифровые интегральные микросхемы в информационно-измерительной аппаратуре.-Л.: Энегргоиздат. Ленингр. отд-ние, 1986, 280 с.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.