![]()

![]()

![]()

![]()

![]()

Данный мультиплексор имеет два адресных входа ![]() и

и ![]() , на

которые могут быть поданы две переменные

, на

которые могут быть поданы две переменные ![]() и

и ![]() . Припишем их слева от соответствующих

логических переменных. Тогда первые два столбца для переменных

. Припишем их слева от соответствующих

логических переменных. Тогда первые два столбца для переменных ![]() и

и ![]() одинаковы

и равны 0 и 0. Это соответствует наличию кода {0 0} на адресных входах

одинаковы

и равны 0 и 0. Это соответствует наличию кода {0 0} на адресных входах ![]() и

и ![]() , т.е. подключению первого информационного

входа D0 на выход мультиплексора. Припишем сверху таблицы истинности

для этих двух столбцов значение информационного входа D0. Аналогично для следующих двух столбцов код на адресных входах

, т.е. подключению первого информационного

входа D0 на выход мультиплексора. Припишем сверху таблицы истинности

для этих двух столбцов значение информационного входа D0. Аналогично для следующих двух столбцов код на адресных входах ![]() и

и ![]() равен {1 0}, что соответствует

подключению входа D1 и т.д.

Значения сигналов, которые должны быть

поданы на информационные входы {

D0 D1 D2 D3} определяют путем сравнение

значений третьей логической переменной

равен {1 0}, что соответствует

подключению входа D1 и т.д.

Значения сигналов, которые должны быть

поданы на информационные входы {

D0 D1 D2 D3} определяют путем сравнение

значений третьей логической переменной ![]() и

реализуемой логической фуекции

и

реализуемой логической фуекции ![]() . Для первых двух

столбцов функция

. Для первых двух

столбцов функция ![]() имеет значение , равное

0. Следовательно на вход D0

необходимо подать сигнал логического 0 .

Для следующих двух столбцов переменная

имеет значение , равное

0. Следовательно на вход D0

необходимо подать сигнал логического 0 .

Для следующих двух столбцов переменная ![]() принимает

последовательно значения 0 и 1. Функция

принимает

последовательно значения 0 и 1. Функция ![]() при

этом тоже принимает последовательно значения 0 и 1, т.е. повторяет её. Поэтому

на вход D1 заводится сама

переменная

при

этом тоже принимает последовательно значения 0 и 1, т.е. повторяет её. Поэтому

на вход D1 заводится сама

переменная ![]() . Аналогично рассуждая,

получаем для входа D2 сигнал

. Аналогично рассуждая,

получаем для входа D2 сигнал ![]() и на входе D3

сигнал логической 1. Схема реализации мажоритарного логического на 3 входа на

мультиплексоре 4:1 приведена на рис. 5.1. Реализованная логическая функция

и на входе D3

сигнал логической 1. Схема реализации мажоритарного логического на 3 входа на

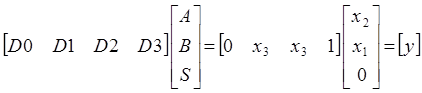

мультиплексоре 4:1 приведена на рис. 5.1. Реализованная логическая функция ![]() , представленная в матричном виде выглядит

следующим образом:

, представленная в матричном виде выглядит

следующим образом:

(5.1)

(5.1)

![]()

В качестве второго

примера рассмотрим процедуру синтеза для сумматора по модулю 2 четырех

логических переменных ![]() на базе двух мультиплексоров

4:1.

на базе двух мультиплексоров

4:1.

Таблица истинности

сумматора по модулю 2 четырех переменных ![]() представлена

табл. 5.2

представлена

табл. 5.2

1D0 1D1 1D2 1D3 2D0 2D1 2D2 2D3

|

|

|

|

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

1 |

|

|

|

|

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

|

|

|

|

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

1 |

|

|

|

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

0 |

1 |

||

|

|

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

0 |

1 |

0 |

1 |

1 |

0 |

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

Мультиплексоры 4:1 имеют два адресных входа,

следовательно, на каждом из них в отдельности может быть реализована только

логическая функция трех переменных. Для реализации логической функции четырех

переменных необходимо дополнительно использовать стробирующие входы мультиплексоров.

Для управления стробирующими входами ![]() мультиплексоров в табл.

5.2 выделим переменную

мультиплексоров в табл.

5.2 выделим переменную ![]() - это наиболее удобно и

наглядно. Из таблицы видно, что переменная

- это наиболее удобно и

наглядно. Из таблицы видно, что переменная ![]() для

первых 8 столбцов принимает значение равное 0, а для следующих столбцов – 1. В

соответствии с этим таблицу 5.2 разделим на две части по границе 0 – 1 для

переменной

для

первых 8 столбцов принимает значение равное 0, а для следующих столбцов – 1. В

соответствии с этим таблицу 5.2 разделим на две части по границе 0 – 1 для

переменной ![]() . Первую часть таблицы 5.2 необходимо

реализовать на одном мультиплексоре, а вторую часть - на другом. Реализуем

первую часть (первые 8 столбцов).

. Первую часть таблицы 5.2 необходимо

реализовать на одном мультиплексоре, а вторую часть - на другом. Реализуем

первую часть (первые 8 столбцов).

Переменной ![]() приписываем слева значение стробирующего

входа

приписываем слева значение стробирующего

входа ![]() первого мультиплексора, которым она

управляет. Остается логическая функция трех переменных

первого мультиплексора, которым она

управляет. Остается логическая функция трех переменных ![]() ,

которая реализуется аналогично примеру, рассмотренному выше. Переменным

,

которая реализуется аналогично примеру, рассмотренному выше. Переменным ![]() и

и![]()

![]() приписываем слева значения

приписываем слева значения ![]() и

и ![]() адресных

входов первого мультиплексора. Тогда первым двум столбцам таблицы

соответствует код {0 0}на

адресных входах

адресных

входов первого мультиплексора. Тогда первым двум столбцам таблицы

соответствует код {0 0}на

адресных входах ![]()

![]() , т.е. подключение первого входа первого

мультиплексора 1D0. Значение сигнала, который необходимо подать на

вход 1D0 определяем по значениям переменной

, т.е. подключение первого входа первого

мультиплексора 1D0. Значение сигнала, который необходимо подать на

вход 1D0 определяем по значениям переменной ![]() и функции

и функции![]() для

этих столбцов. Для первых двух столбцов

для

этих столбцов. Для первых двух столбцов ![]() принимает

последовательно значения 0 и 1 . Функция

принимает

последовательно значения 0 и 1 . Функция ![]() принимает

последовательно те же значения 0 и 1, т.е. повторяет переменную

принимает

последовательно те же значения 0 и 1, т.е. повторяет переменную ![]() . Следовательно на вход 1D0

необходимо завести саму переменную

. Следовательно на вход 1D0

необходимо завести саму переменную ![]() . Аналогично рассуждая

получаем, что на вход 1D1 необходимо подать инвертированное значение

. Аналогично рассуждая

получаем, что на вход 1D1 необходимо подать инвертированное значение ![]() , на вход 1D2 -

, на вход 1D2 -![]() , на 1D3 -

, на 1D3 - ![]() . Таким образом, первая часть таблицы 5.2

реализуется на первом мультиплексоре 4:1.

. Таким образом, первая часть таблицы 5.2

реализуется на первом мультиплексоре 4:1.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.