Для нормальной работы счетчика

необходимо иметь сигнал прямоугольной формы с малым временем нарастания (t01)

и спада (t10). Сигнал, снимаемый с выхода ЗГ, имеет синусоидальную

форму, поэтому необходимо на входе делителя установить формирователь

прямоугольных импульсов. Роль формирователя будут играть два последовательно

включенных инвертора, выполненных на микросхеме КР1531ЛН1 [9]. Для развязки

выходного сопротивления ЗГ и входа ДЧ используем буферный каскад. Выбор этой

микросхемы обусловлен тем, что она имеет наивысшее быстродействие. Питание

микросхемы КР1531ЛН1 осуществляется от стабилизированного источника напряжения

+5 В. время нарастания t01=3,5 нс, время спада t10=38 нс.

Таким образом сигнал ЗГ частотой 45 МГц с выхода буферного каскада поступает на

формирователь. С выхода формирователя сигнал прямоугольной формы поступает на

делитель частоты. Разобьем общий коэффициент деления N=4500 на сомножители. N=![]() . Таким образом, для достижения

необходимого коэффициента деления потребуется четыре двоично-десятичных

синхронных счетчика. Для делителей выберем счетчики ТТЛ серии ИЕ9. Счетчик ИЕ9

имеет предустановочные входы для предварительной установки D-триггеров, которая

осуществляется подачей разного уровня напряжения на вход РЕ(9). При достижении

необходимого коэффициента счета на выходе ТС(13) появляется импульс

положительной полярности. Сигнал поступает на вход С. На входы разрешения счета

СЕР(7) и СЕТ(10) подается напряжение высокого уровня. С приходом десятого

тактового импульса на выходе ТС появляется сигнал высокого импульса. Таким

образом, в счетчике осуществляется деление входной частоты на 10. Для первого

делителя выбираем счетчик серии 1533, как наиболее быстродействующий. для

аналогичного ему второго счетчика выбираем микросхему КМ555ИЕ9. Входы

предустановки обеих микросхем не задействованы [9].

. Таким образом, для достижения

необходимого коэффициента деления потребуется четыре двоично-десятичных

синхронных счетчика. Для делителей выберем счетчики ТТЛ серии ИЕ9. Счетчик ИЕ9

имеет предустановочные входы для предварительной установки D-триггеров, которая

осуществляется подачей разного уровня напряжения на вход РЕ(9). При достижении

необходимого коэффициента счета на выходе ТС(13) появляется импульс

положительной полярности. Сигнал поступает на вход С. На входы разрешения счета

СЕР(7) и СЕТ(10) подается напряжение высокого уровня. С приходом десятого

тактового импульса на выходе ТС появляется сигнал высокого импульса. Таким

образом, в счетчике осуществляется деление входной частоты на 10. Для первого

делителя выбираем счетчик серии 1533, как наиболее быстродействующий. для

аналогичного ему второго счетчика выбираем микросхему КМ555ИЕ9. Входы

предустановки обеих микросхем не задействованы [9].

Таким образом, после прохождения двух делителей частота генератора уменьшается в 10·10=100 раз, то есть она равна 450 кГц. Для делителя на 9 используем тот же счетчик КМ555ИЕ9. Для изменения коэффициента деления с 10 на 9 на входы предустановки необходимо подать число 10-9=1 в двоичной форме, то есть 0001. Для предустановки необходимо, чтобы на входе РЕ был сигнал низкого уровня. Для получения такого сигнала используем микросхему К555ЛА12, в составе которой находится четыре логических элемента И-НЕ. После окончания счета на входе ТС появляется сигнал высокого уровня, который поступает на вход синхронизации следующей микросхемы-делителя и одновременно поступает на входы 1 и 2 логического элемента DD5.1 (К555ЛА12). С выхода 4 DD5.1 сигнал низкого уровня поступает на вход РЕ и разрешает прохождение предустановочного кода. С приходом следующего тактового импульса процесс счета повторяется. Делитель частоты на 5 собран на микросхеме DD6 типа КМ555ИЕ9. Его работа аналогична работе делителя на микросхеме DD4, на предустановочные коды необходимо подать в этом случае число 10-5=0101, что достигается путем подачи напряжения на входы D0 и D2. Сигнал на вход РЕ формируется в элементе DD5.2, включенного по схеме инвертора на выходе DD5.2 присутствует сигнал с частотой 10 кГц.

4.5 Расчет выходного усилителя мощности

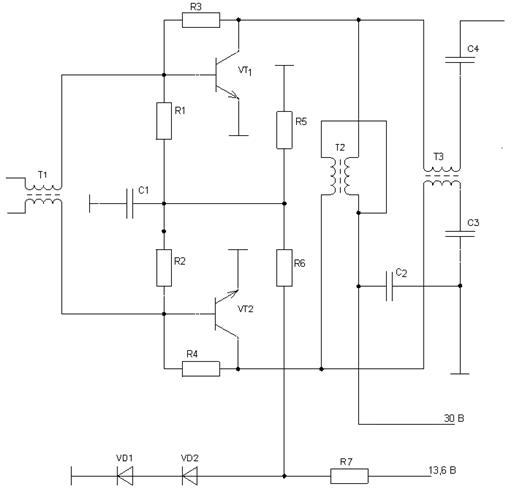

Выбираем принципиальную схему, представленную на рисунке 4.8.

Рис.4.8. Схема электрическая принципиальная выходного усилителя мощности

Исходные данные для расчета оконечного усилителя мощности передатчика с ОМ:

Р1max ном = 100 Вт - максимальная номинальная мощность;

fд = 1,6..30 МГц - диапазон частот;

Кб вх = 0,7.

Расчет выполним по методике изложенной в [7] для одного плеча двухтактного генератора на мощность 50 Вт. Угол отсечки коллекторного тока выбираем равным 90 градусов.

По справочнику [10] выбираем транзистор КТ957А со следующими параметрами:

rнас = 0,1 Ом - сопротивление насыщения;

rб = 0,5 Ом - сопротивление базы;

rэ = 0,1 Ом - сопротивление эмиттера;

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.