Задание №5

Реализация контроллера последовательной селекции

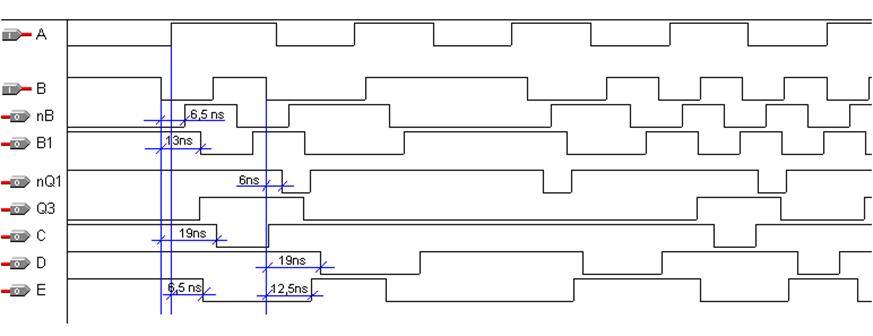

Задание:спроектировать схему контроллера последовательной селекции со следующими временными диаграммами:

|

Рис. 1. Требуемые Временные диаграммы

· Сигнал А – запрос на выбор устройства – асинхронный

· Сигнал B (может появиться в любой момент времени)

· Сигнал С повторяет сигнал B, если E сброшен

· Сигнал D повторяет сигнал B, если E установлен

· Сигнал Е – занято- выставляется при запросе и снимется при освобождении устройства (отправки сигнала B). Установлен если находится в L-уровне, сброшен если в H-уровне.

Сигнала Е - определяет на какой выход транслируется сигнал В (на С, или на D). Изменение Е происходит либо по фронту А, либо по спаду В: по фронту А, если Е сброшен, а по спаду В, если Е установлен.

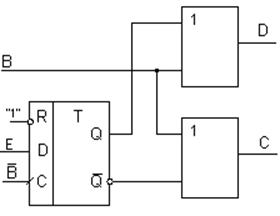

Реализация сигнала E

Вариант 1

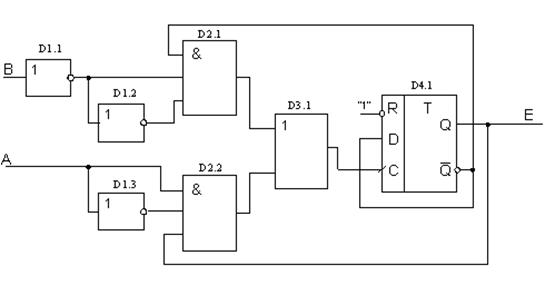

Так как элементы D1 имеют задержки, то на выходах D2 будут формироваться кратковременные импульсы (по фронту A, и по спаду B), которые и будет переключать триггер D3, который непосредственно и формирует сигнал Е.

Рис. 2. Схема реализация сигнала Е (вариант 1)

Вариант 2

Вариант 2

|

Реализация сигналов С и D

Рис 4. Схема реализации сигнала C и D

При реализации этой схемы необходимо обеспечить задержку прихода сигнала В, равную задержке распространения сигнала в триггере.

Вариант 1

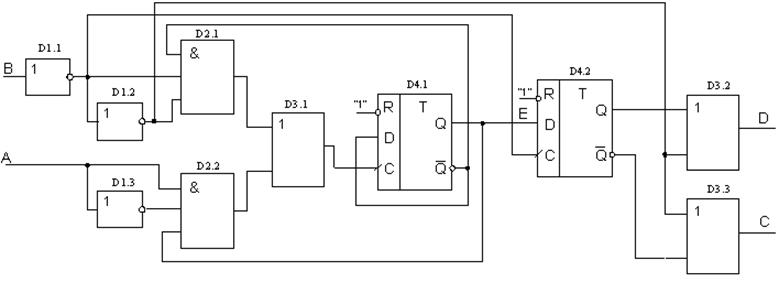

Рис. 5. Схема реализации устройства (вариант1)

|

Об. |

Микросхема |

Функциональное назначение |

tз HL, нс |

tз HL, нс |

f, Мгц |

|

D1 |

74ACTQ04PC |

6 элементов НЕ |

6,5 |

6,5 |

150 |

|

D2 |

74ACTQ08PC |

3 элемента 3И |

6 |

6 |

160 |

|

D3 |

74ACTQ32PC |

4 элемента 2ИЛИ |

6 |

6 |

160 |

|

D4 |

74ACTQ74PC |

2 D-триггера |

6,5 |

6,5 |

150 |

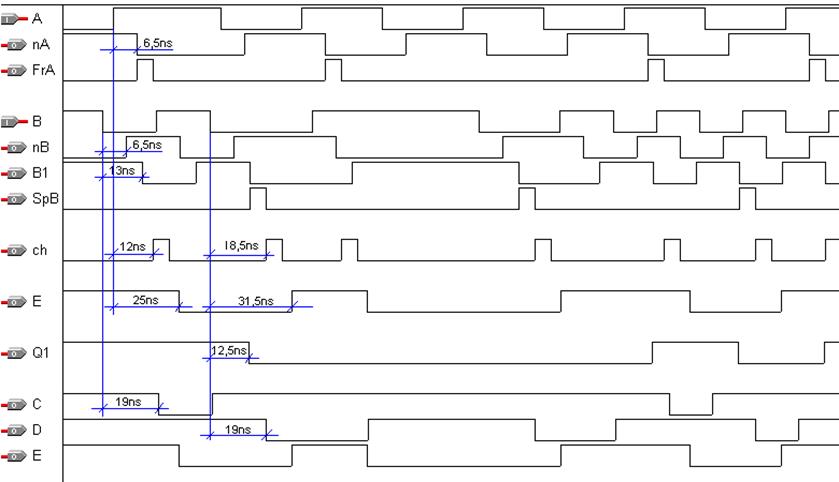

Рис. 6. Временные диаграммы (вариант 1)

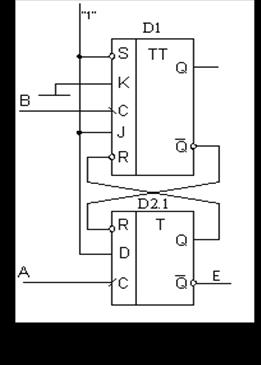

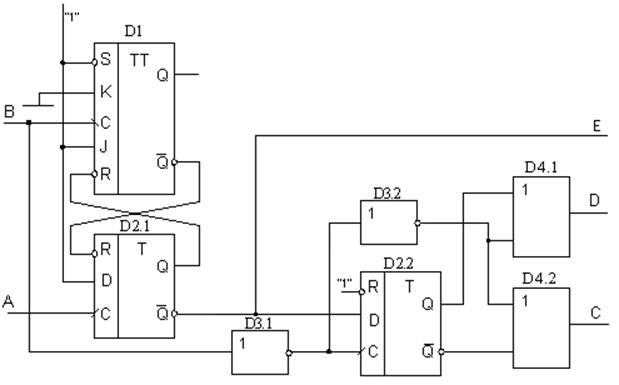

Вариант 2

Рис.7. Схема реализации устройства(вариант 2)

|

Об. |

Микросхема |

Функциональное назначение |

tз HL, нс |

tз HL, нс |

f, Мгц |

|

D1 |

74ACT109PC |

2 JK-триггера |

6 |

7 |

140 |

|

D2 |

74ACTQ74PC |

2 D-триггера |

6,5 |

6,5 |

150 |

|

D3 |

74ACTQ04PC |

6 элементов НЕ |

6,5 |

6,5 |

150 |

|

D4 |

74ACTQ32PC |

4 элемента 2ИЛИ |

6 |

6 |

160 |

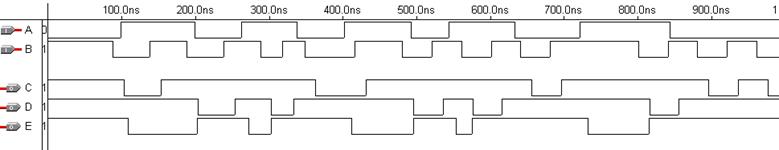

Рис.8. Временные диаграммы (вариант 2)

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.