Лабораторная работа №1

Реализация блока логического устройства

Цель. Реализовать логическое устройство, выполняющее 16 основных логичских команд

Блок логического устройства реализуем в програмном продукте фирмы Altera MAX+plus II 9.4

Так как ЛУ вопринимает на входе два двоичных операнда, то следовательно существует всего 24=16 логичских команд. Эти операции представлены в таблице:

На основе этой таблице составим текстовое описание модуля ЛУ на языке AHDL:

SUBDESIGN lu1

(

f[3..0], a, b : input;

out : output;

)

begin

table

f[], a, b => out;

B"0000", 0, 0 => 0;

B"0000", 0, 1 => 0;

B"0000", 1, 0 => 0;

B"0000", 1, 1 => 0;

B"0001", 0, 0 => 0;

B"0001", 0, 1 => 0;

…

B"1110", 1, 0 => 1;

B"1110", 1, 1 => 0;

B"1111", 0, 0 => 1;

B"1111", 0, 1 => 1;

B"1111", 1, 0 => 1;

B"1111", 1, 1 => 1;

end table;

end;

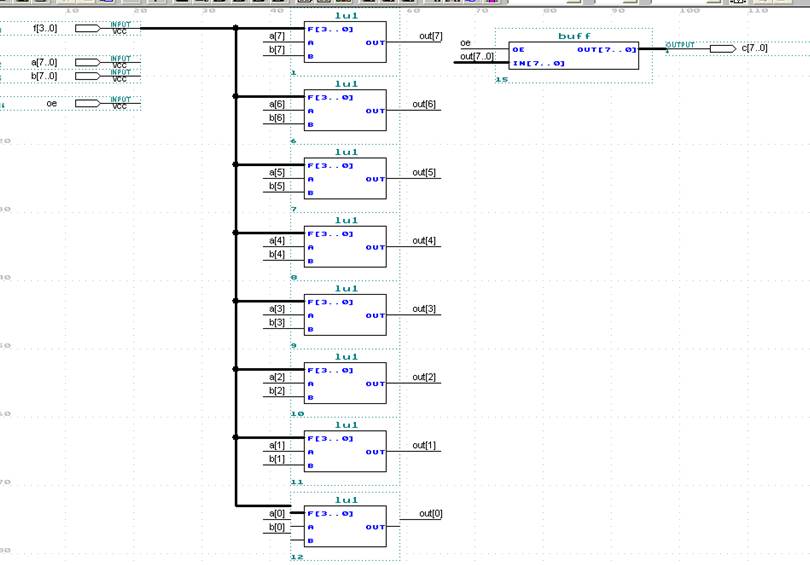

Принципиальная схема логического устройства позволяющего выполнять 16 логических операций над 8-ми разрядными операндами представлена на следующем рисунке:

Текущая логическая операция задается 4-х разрядной микрокомандой:

|

Код микрооперации |

Логическая операция |

|

0000 |

f1 |

|

0001 |

f2 |

|

0010 |

f3 |

|

0011 |

f4 |

|

0100 |

f5 |

|

0101 |

f6 |

|

0110 |

f7 |

|

0111 |

f8 |

|

1000 |

f9 |

|

1001 |

f10 |

|

1010 |

f11 |

|

1011 |

f12 |

|

1100 |

f13 |

|

1101 |

f14 |

|

1110 |

f15 |

|

0111 |

f16 |

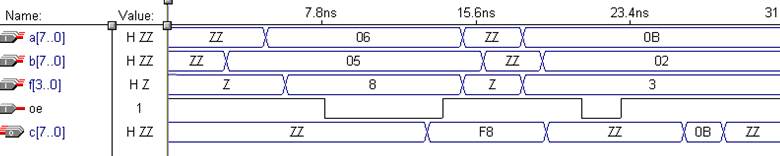

Для тестирования ЛУ создадим временные диаграммы:

Операнды a[7..0] и b[7..0]

Команда f[3..0]

Результат c[7..0]

Сигнал разрешения работы oe

Вывод. Разработано логическое устройство реализующее 16 логических операций над 8-ми разрядными словами. По временным диаграммам определена задержка появления результата относительно сигнала ое равная 5,2 нс.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.