Министерство образования Российской Федерации

Кафедра Вычислительной техники

Расчетно-графическая работа №2

по курсу “Микропроцессорные устройства ”

Выполнил: студенты гр. ВМ-82

Шипилов С.В.

Сапожников С.С

Проверил: ст. преподаватель

Бурдинский И.Н.

Хабаровск 2002

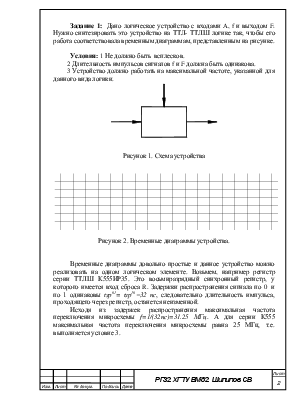

Задание 1: Дано логическое устройство с входами A, f и выходом F. Нужно синтезировать это устройство на ТТЛ- ТТЛШ логике так, чтобы его работа соответствовала временным диаграммам, представленным на рисунке.

Условия: 1 Не должно быть всплесков.

2 Длительность импульсов сигналов f и F должна быть одинакова.

3 Устройство должно работать на максимальной частоте, указанной для данного вида логики.

Рисунок 1. Схема устройства

Рисунок 2. Временные

диаграммы устройства.

Рисунок 2. Временные

диаграммы устройства.

Временные диаграммы довольно простые и данное устройство можно реализовать на одном логическом элементе. Возьмем, например регистр серии ТТЛШ К555ИР35. Это восьмиразрядный синхронный регистр, у которого имеется вход сброса R. Задержки распространения сигнала по 0 и по 1 одинаковы tзр01= tзр10=32 нс, следовательно длительность импульса, проходящего через регистр, останется неизменной.

Исходя из задержек распространения максимальная частота переключения микросхемы f=1/(32нс)=31.25 МГц. А для серии К555 максимальная частота переключения микросхемы равна 25 МГц, т.е. выполняется условие 3.

Рисунок 3. Реализованная схема устройства на микросхеме К555ИР35 (SN74LS273N)

По переднему фронту синхроимпульса f данные на входе A передаются на выход F. По заднему фронту синхроимпульса f на выходе F устанавливается уровень логического “0” не зависимо от сигнала A.

Рисунок 4. Временные диаграммы устройства

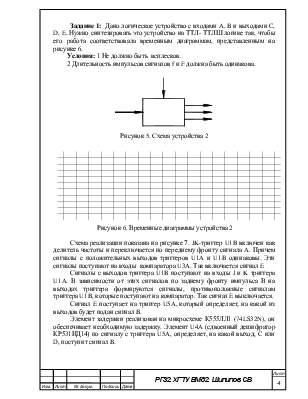

Задание 1: Дано логическое устройство с входами A, B и выходами C, D, E. Нужно синтезировать это устройство на ТТЛ- ТТЛШ логике так, чтобы его работа соответствовала временным диаграммам, представленным на рисунке 6.

Условия: 1 Не должно быть всплесков.

2 Длительность импульсов сигналов f и F должна быть одинакова.

Рисунок 5. Схема устройства 2

Рисунок

6. Временные диаграммы устройства 2

Рисунок

6. Временные диаграммы устройства 2

Схема реализации показана на рисунке 7. JK-триггер U1B включен как делитель частоты и переключается по переднему фронту сигнала A. Причем сигналы с положительных выходов триггеров U1A и U1B одинаковы. Эти сигналы поступают на входы компаратора U3A. Так включается сигнал E

Сигналы с выходов триггера U1B поступают на входы J и K триггера U1A. В зависимости от этих сигналов по заднему фронту импульса В на выходах триггера формируются сигналы, противоположные сигналам триггера U1B, которые поступают на компаратор. Так сигнал E выключается.

Сигнал E поступает на триггер U5A, который определяет, на какой из выходов будет подан сигнал B.

Элемент задержки реализован на микросхеме К555ЛЛ1 (74LS32N), он обеспечивает необходимую задержку. Элемент U4A (сдвоенный дешифратор КР531ИД14) по сигналу с триггера U5A, определяет, на какой выход, C или D, поступит сигнал B.

Микросхемы U8A, U4A имеют одинаковую задержку распространения по нулю и единице, что обеспечивает неизменную длительность сигнала.

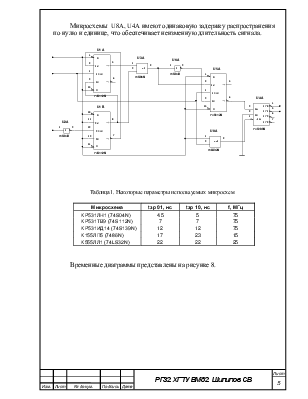

Таблица1. Некоторые параметры используемых микросхем

Таблица1. Некоторые параметры используемых микросхем

|

Микросхема |

tзр 01, нс |

tзр 10, нс |

f, МГц |

|

КР531ЛН1 (74S04N) |

4.5 |

5 |

75 |

|

КР531ТВ9 (74S112N) |

7 |

7 |

75 |

|

КР531ИД14 (74S139N) |

12 |

12 |

75 |

|

К155ЛП5 (7486N) |

17 |

23 |

15 |

|

К555ЛЛ1 (74LS32N) |

22 |

22 |

25 |

Временные диаграммы представлены на рисунке 8.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.