Обобщение этого процесса называется опережающей засылкой. Его можно использовать в вычислительной машине повсюду, чтобы ускорить устранение помех. Что нужно?

а) много фиксаторов на ступенях конвейеров;

б) фиксаторы надо научить запоминать (если данных нет) индексом или тегом (указателем) за вырабатывающую их ступень;

в) после завершения работы ступени по задержанной команде надо проверить: нет ли в каком-нибудь из фиксаторов тега с ее идентификатором, и если есть, то соответствующая ступень получает копию данных.

г) возобновляется выполнение всех задержанных команд и движение по конвейеру.

Все это работает хорошо не только в обычных, но и в суперскалярных архитектурах (параллелизм в конвейерах выполнения команд). И даже в значительной степени под них и разрабатывалось. А примеры? Pentium! MC68060! Сигнальные процессоры!

4.3. Примеры применения конвейеров.

Самое простое – привести структурные (функциональные схемы самых распространенных процессоров в мире ПК: Pentium и MC68…

Вот они.

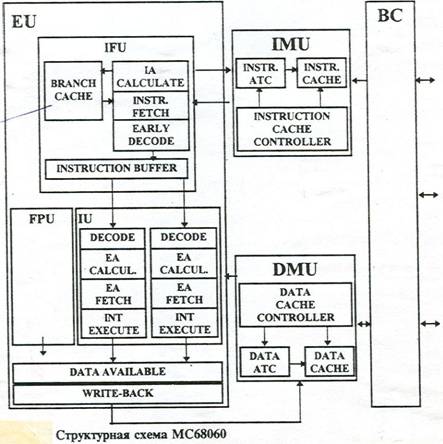

Структура МС68060

Структурная схема МС68060 приведена на рис. выше.

Основными узлами МС68060 являются:

· Исполнительное устройство (Execution Unit –EU);

· Устройство памяти инструкций (Instruction Memory Unit –IMU);

· Устройство памяти данных (Data Memory Unit –DMU);

· Контроллер магистрали (BUS CONTROLLER –BC).

Исполнительное устройство (EU) состоит из:

· устройства выборки инструкций (Instruction Fetch Unit – IFU);

· целочисленного устройства (Integer Unit -IU);

· устройства с плавающей точкой (Floating Point Unit –FPU).

Устройство памяти инструкций (IMU) состоит из:

· кэша адресных трансляций инструкций (Instruction ATC);

· кэша инструкций (Instruction Cache);

· контроллера кэша инструкций (Instruction Cache Controller).

Устройство памяти данных (DMU) состоит из:

· кэша адресных трансляций данных (Data ATC);

· кэша данных (Data Cache);

· контроллера кэша данных (Data Cache Controller).

Устройство памяти инструкций (IMU) и устройство памяти данных (DMU) работают по раздельным внутрикристальным магистралям с EU и BC.

Устройство выборки инструкций исполнительного устройства состоит из четырехкаскадного конвейера извлечения инструкций, кэша ветвлений и логики взаимодействия с кэшем ветвлений. Конвейер извлечения инструкций обеспечивает предварительное извлечение до момента действительного использования инструкций конвейером обработки.

1-й каскад – вычисление исполнительного адреса – IA CALCULATE- обеспечивает вычисление виртуального адреса инструкции.

2-й каскад – извлечение инструкции INSTRUCTION FETCH, является главным в конвейере.

3-й каскад – предварительное декодирование EARLE DECODE. В нем происходит декодирование с целью получения информации об управлении конвейером.

4-й каскад – буфер инструкций INSTRUCTION BUFFER. Представляет собой простую буферную память, где инструкция и ее управляющая информация хранятся до момента их выборки конвейером обработки целочисленного устройства.

Кэш ветвлений опрашивается на наличие достоверного входа ветвлений после генерации каждого адреса в конвейере извлечения инструкций. Если совпадение не произойдет, то конвейер продолжит последовательную выборку.

Целочисленное устройство исполнительного устройства состоит из:

- двух целочисленных конвейеров обработки;

- логики для взаимодействия с FPU;

- логики управления данными.

Суперскалярное устройство двух конвейеров обеспечивает одновременное выполнение двух команд. Логика управления IU выбирает две команды из буфера инструкций IFU в каждом периоде тактовой частоты, останавливаясь только, если информация команды недостаточна, или, если существуют условия остановки конвейера обработки.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.