6 Параллельный оператор конкретизации компонента

Общий вид оператора конкретизации компонента (оператора создания экземпляра компонента):

метка: имя компонента

[generic (список параметров);]

[portmap(список портов)];

Этот оператор употребляется для структурной организации проекта. Часть схемы (подсхема) описывается как компонент (component), имеющий имя (name). Одна и та же подсхема может входить в схему несколько раз, однако, при этом она имеет различные связи. Чтобы описать эти связи, употребляется оператор создания экземпляра компонента (оператор конкретизации компонента), т.е. имеется в виду конкретизация связей данной подсхемы.

Соответствие портов при создании экземпляров компонентов может быть осуществлено:

• позиционным сопоставлением;

• ключевым соответствием, с использованием оператора =>

Приведём пример ключевого соответствия портов при создании экземпляров компонентов, интерфейс которых описан следующим образом:

entity A is

port (x1: in bit; y1: out bit) ;

end A;

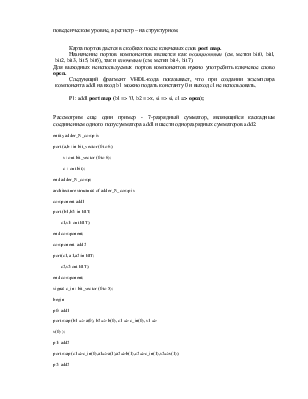

Тогда согласно схеме на рис. 6.1 ключевое соответствие портов при создании экземпляров компонентов будет выглядеть следующим образом:

p1: A port map (xl => xl, yl=>w);

p2: В port map (x2 => w, y2=>z);

p3: С port map (y3=>v, x3 => z);

Сделаем пояснения. При создании экземпляра компонента А портам xl, yl компонента А ставятся в соответствие сигналы xl, w. При создании экземпляра компонента В портам х2, у2 компонента В ставятся в соответствие сигналы w, z. При ключевом соответствии порядок перечисления портов не играет роли, поэтому при ключевом соответствии портов можно сначала указать выходной порт, как это сделано при создании экземпляра компонента С.

Рис.6.1. Конкретизация (создание экземпляров) компонентов

Пример позиционного сопоставления (соответствия) портов при создании экземпляров компонентов.

p1: A portmap(xl,w); -- позиционное соответствие

р2: В portmap(w,z); -- позиционное соответствие

рЗ: С portmap(z,v); -- позиционное соответствие

|

|

Рис.6.2. Сдвиговый регистр

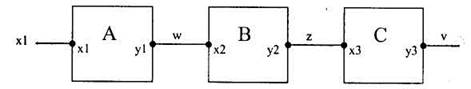

Рассмотрим 8-разрядный сдвиговый регистр (рис.6.2), в состав которого входит восемь подсхем D-триггеров (элементов памяти). D-триггер имеет имя DFF.

Приведём поведенческое(т.е. функциональное) описание D-триггера на языке VHDL:

entity DFF is

port (

RSTn, CLK, D : in bit;

Q : out bit);

end DFF;

architecture RTL of DFF is

; begin

process (RSTn, CLK)

begin

if (RSTn = '0') then Q <= '0';

elsif (CLK'event and CLK = '1') then Q <= D;

end if;

end process;

end RTL;

Теперь опишем сдвиговый регистр SHIFT, в котором триггер будет использован как компонент:

entity SHIFT is

port (

RSTn, CLK, SI : in bit;

SO : out bit);

end SHIFT;

architecture RTL1 of SHIFT is

component DFF

port (

RSTn, CLK, D : in bit;

Q : out bit);

end component;

signal T : bit_vector(6 downto 0);

begin

bit7 : DFF

port map (RSTn => RSTn, CLK => CLK, D => SI, Q => T(6));

bit6 : DFF

port map (RSTn, CLK, T(6), T(5));

bit5 : DFF

port map (RSTn, CLK, T(5), T(4));

bit4 : DFF

port map (CLK => CLK, RSTn => RSTn, D => T(4), Q => T(3));

bit3 : DFF

port map (RSTn, CLK, T(3), T(2));

bit2 : DFF

port map (RSTn, CLK, T(2), T(1));

bit1 : DFF

port map (RSTn, CLK, T(1), T(0));

bit0 : DFF

port map (RSTn, CLK, T(0), SO);

end RTL1;

Схема SHIFT задает сдвиговый регистр - каскадное соединение D-триггеров (элементов памяти)..

Компонент DFF конкретизирован (упомянут) восемь раз, чтобы получить сдвиговый регистр.

Каждый оператор создания экземпляра компонента должен иметь метку. Метки играют роль имен элементов схемы. Здесь следует заметить, что триггер описан на поведенческом уровне, а регистр – на структурном.

Карта портов дается в скобках после ключевых слов portmap.

Назначение портов компонентов является как позиционным (см. метки bit0, bitl, bit2, bit3, bit5, bit6), так и ключевым (см. метки bit4, bit7).

Для выходных неиспользуемых портов компонентов нужно употребить ключевое слово open.

![]()

![]() Следующий

фрагмент VHDL-кода показывает, что при создании экземпляра

компонента addl на вход b1 можно подать константу 0 и выход cl не использовать.

Следующий

фрагмент VHDL-кода показывает, что при создании экземпляра

компонента addl на вход b1 можно подать константу 0 и выход cl не использовать.

P1: addl port map (bl => '0', b2 =>х, si => si,cl => open);

Рассмотрим еще один пример - 7-разрядный сумматор, являющийся каскадным соединением одного полусумматора addl и шести одноразрядных сумматоров add2.

entity adder_N_comp is

port (a,b : in bit_vector (0 to 6);

s : out bit_vector (0 to 6);

c : out bit);

end adder_N_comp;

architecture structural of adder_N_comp is

component add1

port (b1,b2: in BIT;

c1,s1: out BIT);

end component;

component add2

port(c1, a1,a2:in BIT;

c2,s2:out BIT);

end component;

signal c_in : bit_vector (0 to 5);

begin

p0: add1

port map (b1 => a(0), b2 => b(0), c1 => c_in(0), s1 =>

s(0) );

p1: add2

port map (c1=>c_in(0),a1=>a(1),a2=>b(1),c2=>c_in(1),s2=>s(1));

p2: add2

port map (c1=>c_in(1),a1=>a(2),a2=>b(2),c2=>c_in(2),s2=>s(2));

p3: add2

port map (c1=>c_in(2),a1=>a(3),a2=>b(3),c2=>c_in(3),s2=>s(3));

p4: add2

port map (c1=>c_in(3),a1=>a(4),a2=>b(4),c2=>c_in(4),s2=>s(4));

p5: add2

port map (c1=>c_in(4),a1=>a(5),a2=>b(5),c2=>c_in(5),s2=>s(5));

p6: add2

port map (c1=>c_in(5),a1=>a(6),a2=>b(6),c2=>c,s2=>s(6));

end structural;

Схемы сдвигового регистра и сумматора являются регулярными и могут быть описаны более компактно с помощью оператора генерации Generate.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.