- 24 – Channel Digital I/O – параллельный периферийный адаптер;

- D/D Converter – формирователи уровня входных/выходных сигналов.

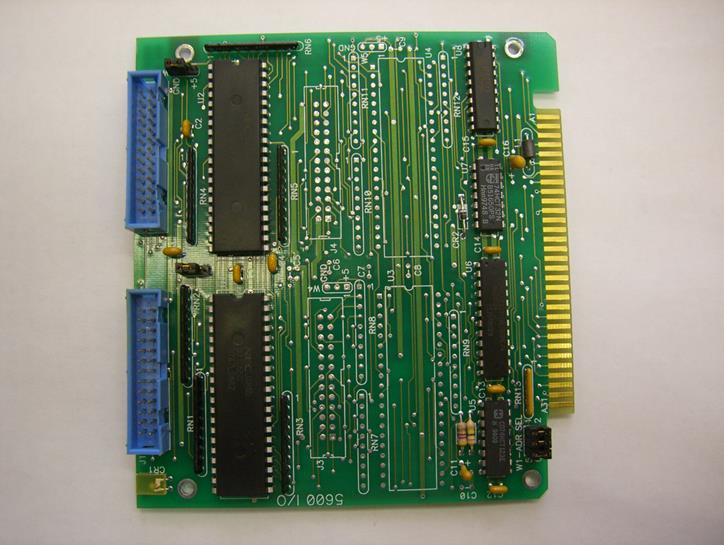

Рисунок 3

Рисунок 4

В таблице 1 показаны основные характеристики плат расширения на 24, 48 и 144 входов/выходов соответственно.

Таблица 1

Тип платы |

Количество входов/выходов |

Нагрузочная способность |

Дополнительные функции |

Внешние разъемы |

|

5600 |

24 |

24 mA sink 15 mA source |

2 interrupt input |

1x50-pin Opto-22 |

PCL-731 |

48 |

24 mA sink 15 mA source |

2 interrupt input |

2x50-pin Opto-22 |

PCL-722 |

144 |

12 mA sink 8 mA source |

2 interrupt input |

6x50-pin Opto-22 |

3 Структура параллельного периферийного адаптера (ППА)

Микросхема intel 8255 параллельного периферийного адаптера представляет собой программируемое устройство ввода/вывода параллельной информации, применяется в качестве элемента ввода/вывода общего назначения, сопрягающего различные типы периферийных устройств с магистралью данных систем обработки информации.

Условное графическое обозначение микросхемы приведено на рисунке 5, назначение выводов в таблице 2, структурная схема показана на рисунке 6.

Рисунок 5

Таблица 2

Вывод |

Обозначение |

Тип вывода |

Функциональное назначение выводов |

|||

|

1 – 4 37 – 40 5 6 7 8, 9 10 –13 14 – 17 18 – 25 26 27 – 34 35 36 |

А3 – А0, А7 – А4

GND А1, А0 С7 – С4 С0 – С3 В0 – В7 Uсс D0 – D7 SR

WR |

Входы/выходы Входы/выходы Вход Вход – Вход Входы/выходы Входы/выходы Входы/выходы – Входы/выходы Вход Вход |

Информационный канал А Чтение информации Выбор микросхемы ОбщийСтаршие разряды информационного канала С Младшие разряды информационного канала С Информационный канал В Напряжение питания + 5В+5% Канал данных Установка в исходное состояние Запись информации |

![]()

![]()

![]() Выводы 26 и 7 микросхемы представляют собой выводы питания.

Питание осуществляется напряжением + 5В+5%. Выводы 27 – 34 образуют 8-разрядный

двунаправленный канал данных который подключается к шине данных

микропроцессорной системы, а при использовании микросхемы ППА в платах

расширения – к шине ISA. Выводы А0, А1, RD, WR, CS –

системные управляющие сигналы обеспечивающие запись/чтение информации по каналу

D ППА. SR – сигнал сброса, устанавливает ППА в режим 0 все

каналы на ввод информации.

Выводы 26 и 7 микросхемы представляют собой выводы питания.

Питание осуществляется напряжением + 5В+5%. Выводы 27 – 34 образуют 8-разрядный

двунаправленный канал данных который подключается к шине данных

микропроцессорной системы, а при использовании микросхемы ППА в платах

расширения – к шине ISA. Выводы А0, А1, RD, WR, CS –

системные управляющие сигналы обеспечивающие запись/чтение информации по каналу

D ППА. SR – сигнал сброса, устанавливает ППА в режим 0 все

каналы на ввод информации.

Рисунок 6

Информационные каналы А, В и С обеспечивают ввод/вывод логических сигналов по 24 линиям. Уровень логического “0” – не более 0,4В, уровень логической “1”– не менее 2,4В. Следует отметить, что канал С разбивается на два подканала младший С0 – С3 и старший С4 – С7 которые могут настраиваться независимо на ввод или вывод информации.

Обмен информацией между магистралью данных систем и микросхемой ППА осуществляется через 8-разрядный двунаправленный трехстабильный канал данных (D). Для связи с периферийными устройствами используется 24 линии ввода/вывода, сгруппированные в три 8-разрядных канала А, В, С, направление передачи информации и режимы работы которых определяются программным способом.

Микросхема может функционировать в трех основных режимах. В режиме 0 обеспечивается возможность асинхронной программно управляемой передачи данных через два независимых 8-разрядных канала А и В и два 4-разрядных канала С.

В режиме 1 обеспечивается возможность ввода или вывода информации в/или из периферийного устройства через два независимых 8-разрядных канала А и В по сигналам квитирования. При этом линии канала С используются для приема и выдачи сигналов управления обменом.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.