Министерство Путей Сообщения

Российской Федерации

ПетербургскийГосударственный Университет

Путей Сообщения

Кафедра: “Автоматика и телемеханика на железнодорожном транспорте”.

Отчет по лабораторная работе 3 по курсу «Микропроцессорные системы»:

“TIMER”.

Вариант №18

Выполнил студент

Группы АТ-101

Уваров Е.Н.

Санкт-Петербург

2004

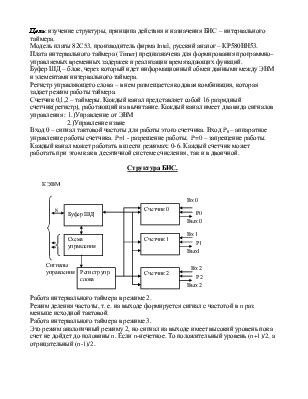

Цель: изучение структуры, принципа действия и назначения БИС – интервального таймера.

Модель платы 82C53, производитель фирма Intel, русский аналог – КР580ВН53. Плата интервального таймера (Timer) предназначена для формирования программно-управляемых временных задержек и реализации времязадающих функций.

Буфер ШД – блок, через который идет информационный обмен данными между ЭВМ и элементами интервального таймера.

Регистр управляющего слова – в нем размещается кодовая комбинация, которая задает режим работы таймера.

Счетчик 0,1,2 – таймеры. Каждый канал представляет собой 16 разрядный счетчик(регистр), работающий на вычитание. Каждый канал имеет два вида сигналов управления : 1.)Управление от ЭВМ

2.)Управление извне

Вход 0 – сигнал тактовой частоты для работы этого счетчика. Вход P0 – аппаратное управление работы счетчика. P=1 - разрешение работы, P=0 – запрещение работы.

Каждый канал может работать в шести режимах: 0-6. Каждый счетчик может работать при этом как в десятичной системе счисления, так и в двоичной.

Структура БИС.

|

Работа интервального таймера в режиме 2.

Режим деления частоты, т. е. на выходе формируется сигнал с частотой в n раз меньше исходной тактовой.

Работа интервального таймера в режиме 3.

Это режим аналогичный режиму 2, но сигнал на выходе имеет высокий уровень пока счет не дойдет до половины n. Если n-нечетное. То положительный уровень (n+1)/2, а отрицательный (n-1)/2.

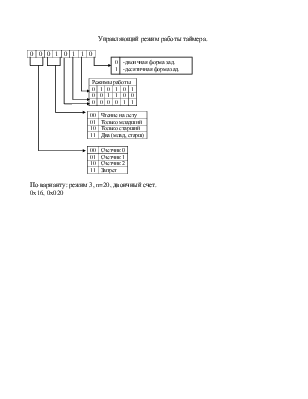

Управляющий режим работы таймера.

|

|

|

|

|

0 |

|

|

|

![]()

![]()

![]()

![]()

![]()

![]()

![]()

![]()

|

Режимы работы |

|||||

|

0 |

1 |

0 |

1 |

0 |

1 |

|

0 |

0 |

1 |

1 |

0 |

0 |

|

0 |

0 |

0 |

0 |

1 |

1 |

|

|

Чтение на лету |

|

01 |

Только младший |

|

10 |

Только старший |

|

11 |

Два (млад, старш) |

|

|

Счетчик 0 |

|

01 |

Счетчик 1 |

|

10 |

Счетчик 2 |

|

11 |

Запрет |

По варианту: режим 3, n=20, двоичный счет.

0x16, 0x020

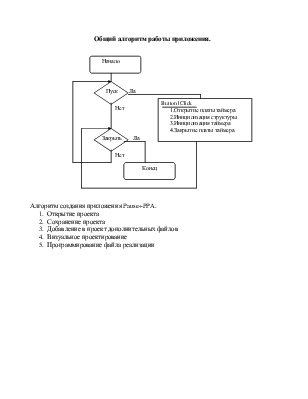

Общий алгоритм работы приложения.

|

Алгоритм создания приложения Pause+PPA.

1. Открытие проекта

2. Сохранение проекта

3. Добавление в проект дополнительных файлов

4. Визуальное проектирование

5. Программирование файла реализации

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.