С помощью этой таблицы легко определить, что

![]()

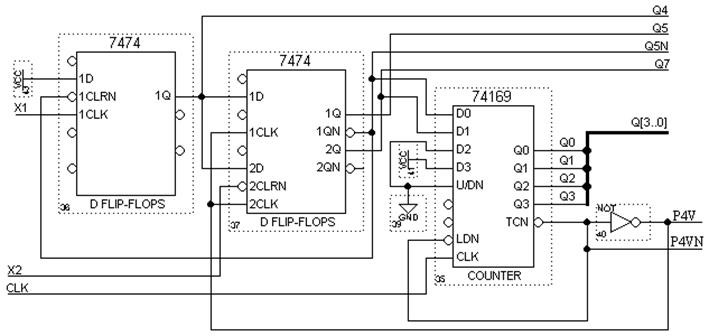

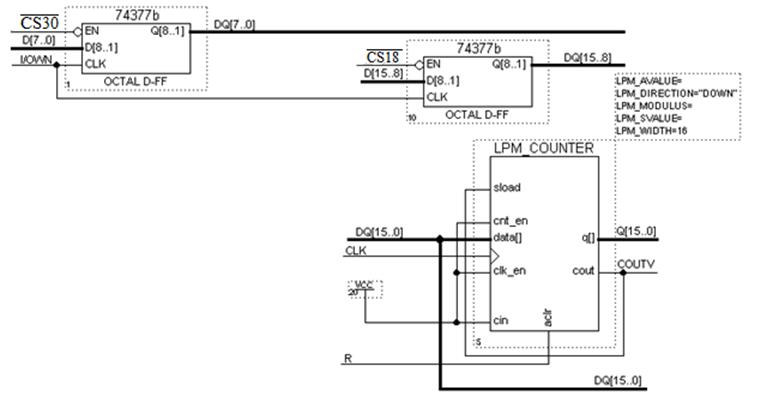

По этим функциям построена схема на МЭ фирмы Altera, представленная на рисунке 6, а на рисунке 7 - временные диаграммы, поясняющие работу схемы.

Рис.6. Счётчик по модулю 9, 10, 11.

Рис.7. Временные диаграммы работы счётчика по модулю 9, 10, 11.

Определим

длительность двух переходных процессов, формирующих сигналы ![]() и сигналы данных

и сигналы данных ![]() :

:

![]()

а формирование данных:

![]()

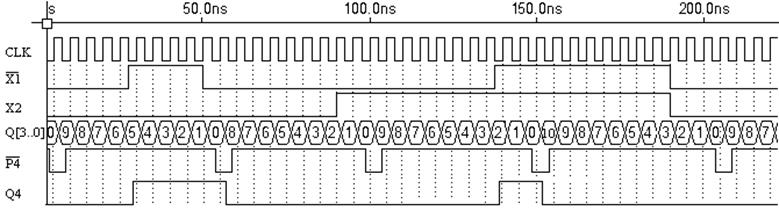

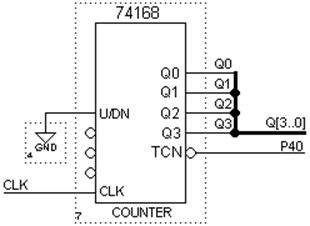

Счетчик по модулю 10 строится на макроэлементе 74168, который сам и является счетчиком по модулю 10. Загрузка в таком счётчике отсутствует. На рисунке 8 изображена схема счётчика, а на рисунке 9 – временные диаграммы работы делителя.

Рис.8.

Делитель на ![]() на МЭ фирмы Altera.

на МЭ фирмы Altera.

Рис.9. Временные диаграммы работы

делителя на ![]()

Для

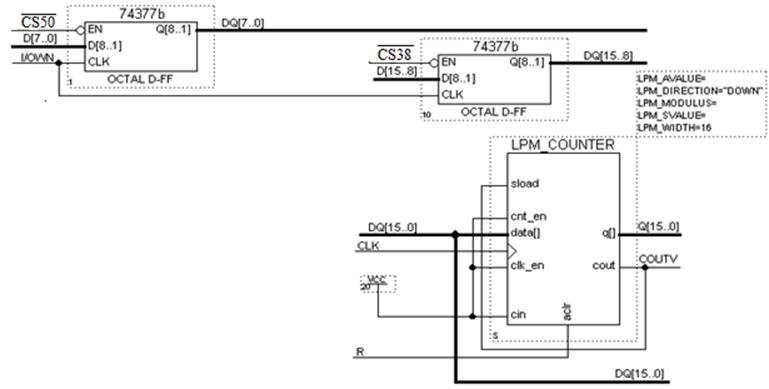

построения делителя на МЭ фирмы Altera

используются счетчики из папки lpm:

16-разрядный счетчик lpm_counter с синхронной загрузкой данных. На

рисунке 6 показана схема 16-разрядного счетчика. Модуль пересчета ![]() этого счетчика определяется

соотношением

этого счетчика определяется

соотношением ![]() , т.е. он задается параллельной

записью в счетчик числа

, т.е. он задается параллельной

записью в счетчик числа ![]() . Число

. Число ![]() – двухбайтовое, содержащее мдадший

байт

– двухбайтовое, содержащее мдадший

байт ![]() и старший байт

и старший байт ![]() , хранящиеся в памяти в соседних

ячейках. Оба байта должны быть записаны в регистры памяти 74377b. По команде

, хранящиеся в памяти в соседних

ячейках. Оба байта должны быть записаны в регистры памяти 74377b. По команде ![]() вырабатывается системный сигнал

управления

вырабатывается системный сигнал

управления ![]() , а дешифратор адресных сигналов

внешних устройств вырабатывает сигнал

, а дешифратор адресных сигналов

внешних устройств вырабатывает сигнал ![]() , который разрешает запись младшего

байта

, который разрешает запись младшего

байта ![]() в регистр; запись производится

положительным перепадом сигнала

в регистр; запись производится

положительным перепадом сигнала ![]() . Аналогичным образом по команде

. Аналогичным образом по команде ![]() записывается старший байт данных

записывается старший байт данных ![]() в регистр 74377b.

в регистр 74377b.

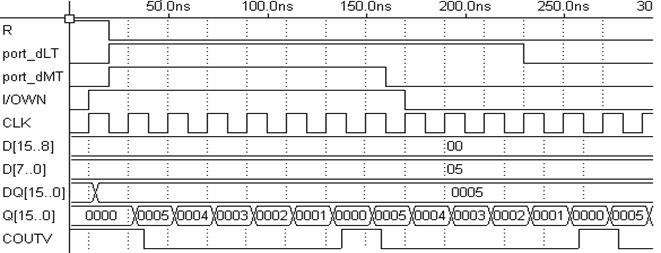

Временные

диаграммы работы счетчика представлены на рисунке 11. После загрузки младшего

байта ![]() и старшего байта

и старшего байта ![]() , которая разрешается сигналом

, которая разрешается сигналом![]() , возникающем в нулевом состоянии

счетчика, счетчик начинает считать до нуля, после чего снова произойдет

загрузка. На рисунке запись младшего и старшего байта осуществляется

одновременно, реально же запись младшего и старшего байта происходит в разные

моменты времени.

, возникающем в нулевом состоянии

счетчика, счетчик начинает считать до нуля, после чего снова произойдет

загрузка. На рисунке запись младшего и старшего байта осуществляется

одновременно, реально же запись младшего и старшего байта происходит в разные

моменты времени.

Схема

16-разрядного делителя частоты используется как в неподвижном канале (на

тактовый вход подается сигнал с выхода делителя на ![]() ), так и в подвижном канале (на

тактовый вход подается сигнал с выхода делителя на

), так и в подвижном канале (на

тактовый вход подается сигнал с выхода делителя на ![]() ). Выходные сигналы счетчиков

). Выходные сигналы счетчиков ![]() являются сигналами

являются сигналами ![]() и

и ![]() .

.

Рис.10. Схема

16-разрядного делителя на ![]() .

.

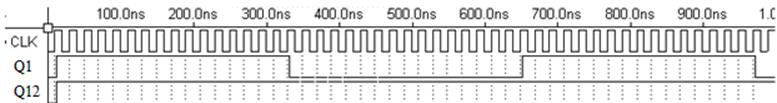

Рис.11. Временные диаграммы 16-разрядного делителя.

Макроэлемент

счетчика используется в режиме делителя на ![]() ; для

; для ![]() выходной сигнал снимается с выхода

выходной сигнал снимается с выхода ![]() (схема представлена на рисунке 12, а

временные диаграммы – на рисунке 13). Эта же схема формирует сигнал частоты

(схема представлена на рисунке 12, а

временные диаграммы – на рисунке 13). Эта же схема формирует сигнал частоты ![]() для опроса шифратора клавиатуры, при

этом коэффициент деления

для опроса шифратора клавиатуры, при

этом коэффициент деления

Тогда

![]()

если использовать 16-разрядный

счетчик с выходом ![]() , при этом частота выходного сигнала

, при этом частота выходного сигнала

|

|

Рис.12. Делитель на ![]() и

и ![]() .

.

Рис.13. Временные

диаграммы работы делителя на ![]() и

и ![]() .

.

Рис.14. Схема

16-разрядного делителя на ![]()

Делитель на ![]() строится по такому же принципу, что

и делитель на

строится по такому же принципу, что

и делитель на ![]() (16-разрядный счетчик с записью

двухбайтовых чисел). На вход делителя поступает сигнал частоты

(16-разрядный счетчик с записью

двухбайтовых чисел). На вход делителя поступает сигнал частоты ![]() , выходной сигнал делителя -

, выходной сигнал делителя - ![]() . Схема делителя на

. Схема делителя на ![]() показана на рисунке 14.

показана на рисунке 14.

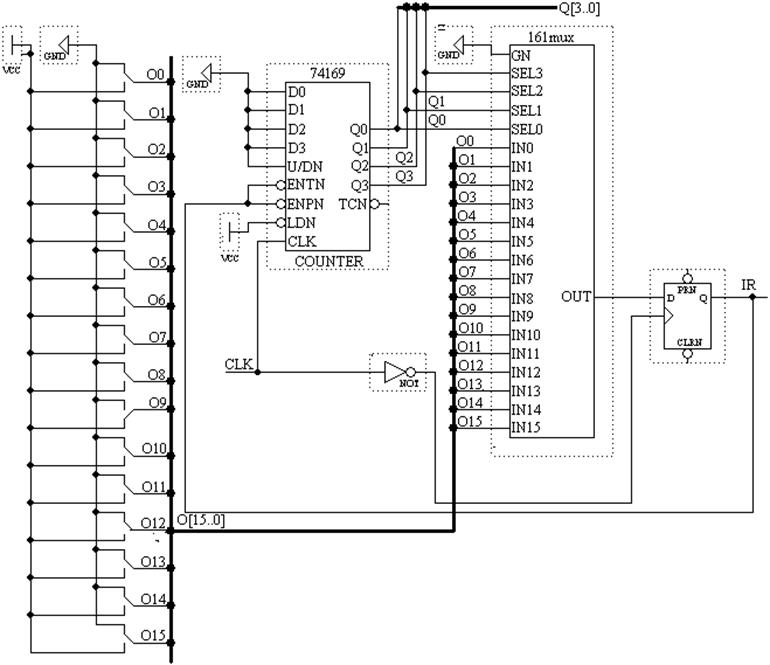

Для управления имитатором используются 16 клавиш, каждой из которых приписан свой 4-разрядный двоичный код. При нажатии любой клавиши контроллер клавиатуры должен выдавать двоичный код этой клавиши и флаг клавиатуры, указывающий сигнал запроса прерывания IR (InterruptRequest). На рисунке 16 изображена схема шифратора клавиатуры, содержащая счетчик по модулю 16 (74169) и мультиплексор 16®1 (161mux).

Рис.12. Схема шифратора клавиатуры.

При замыкании

клавиши ![]() выходной сигнал

выходной сигнал ![]() мультиплексора примет значение 1 в момент времени, когда

счетчик установится в состояние

мультиплексора примет значение 1 в момент времени, когда

счетчик установится в состояние ![]() , что приведет к появлению значения

сигнала

, что приведет к появлению значения

сигнала ![]() и блокировке счета. Пока клавиша

нажата, счетчик выдает число

и блокировке счета. Пока клавиша

нажата, счетчик выдает число ![]() , а D-триггер – сигнал

, а D-триггер – сигнал ![]() . При отпускании клавиши сигнал

. При отпускании клавиши сигнал ![]() установится в

установится в ![]() и счетчик продолжит счет. Чем ниже частота задающего

генератора, тем надежнее исключается «дребезг» контактов клавиш. На частоте

генератора

и счетчик продолжит счет. Чем ниже частота задающего

генератора, тем надежнее исключается «дребезг» контактов клавиш. На частоте

генератора ![]() «дребезг» надежно устраняется. На

рисунке 17 – временные диаграммы для случая, когда нажата клавиша с номером 9.

«дребезг» надежно устраняется. На

рисунке 17 – временные диаграммы для случая, когда нажата клавиша с номером 9.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.