|

|

|

|

|

||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

Спроектировать на микропроцессоре (МП) 1821ВМ85 имитатор сигналов, отраженных от движущейся цели. Параметры имитатора:

– периоды

следования зондирующих импульсов ![]() (мс),

(мс), ![]() – скорости движения цели

– скорости движения цели ![]() (км/ч),

(км/ч), ![]() ;

;

– частота

тактового сигнала ![]() (МГц).

(МГц).

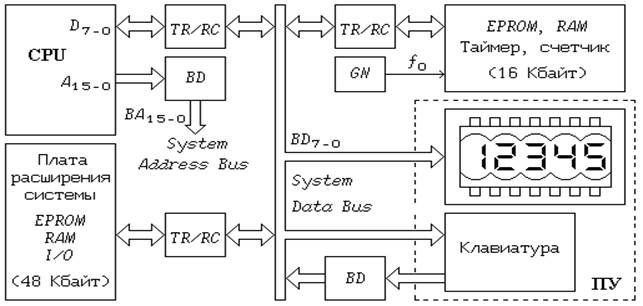

Имитатор реализовать в виде микроконтроллера, структурная схема которого изображена на рисунке 1: CPU (CentralProcessingUnit) – центральный процессор, GN (Generator) – генератор тактовых сигналов, TR/RC (Transmitter/Receiver) – приемопередатчик, BD(BusDriver) – шинный драйвер, EPROM (ErasableProgrammableReadOnlyMemory) – постоянное запоминающее устройство (ПЗУ) со стиранием ультрафиолетовыми лучами, RAM (RandomAccessMemory) – оперативное запоминающее устройство (ОЗУ), I/O (Input/Output) – устройства ввода-вывода, внешние устройства. Выбрать ПЛИС фирмы Altera для аппаратной части имитатора, построить схему и разработать программное обеспечение.

Пульт

управления (ПУ) состоит из клавиатуры и дисплея. Значения параметров ![]() и

и ![]() задаются с клавиатуры. Дисплей

выполняется на 5-разрядном 7-сегментном светодиодном индикаторе АЛС328В.

задаются с клавиатуры. Дисплей

выполняется на 5-разрядном 7-сегментном светодиодном индикаторе АЛС328В.

Управление дисплеем осуществить при помощи специализированной микросхемы ICM7218C.

Рис. 1. Структурная схема микроконтроллера.

Имитатор радиолокационного сигнала предназначен для проверки работоспособности и настройки устройств обработки сигналов в радиолокационных системах. На рисунке 2a изображена структурная схема имитатора радиолокационных сигналов: G – сигнал, из которого формируется зондирующий импульс dG; GV – сигнал, из которого формируется импульс dGV отраженный от движущейся цели. Эти сигналы имеют период повторения T = M×T0, где M = M0×M1, T0 = 1/f0 – период тактового сигнала H (рис. 1.1, б).

|

|

|

|

а |

б |

|

Рис.2. Схема имитатора радиолокационного сигнала. |

|

Задачей имитатора является сдвиг временного положения импульсов dGV относительно импульсов dG на время T0 при воздействии каждого перехода сигнала x1 с 1 на 0 (сдвиг производится по команде dx1 = 1, где d – оператор логического дифференцирования [1]). Направление сдвига определяется значением сигнала x2. Если сигнал x1 имеет постоянную частоту Fj = F/Mj, то сигнал dGV будет перемещаться по отношению к сигналу dG с постоянной скоростью, что соответствует имитации цели, движущейся с фиксированной радиальной скоростью.

Основным

узлом такого имитатора является счетчик с программируемым модулем пересчета MV = M0, M0

– 1, M0 + 1 [2]. Действительно, если при dx1

= 0 модуль пересчета MV = M0, то частоты сигналов G и GV равны, разность их фаз (разность ![]() временных положений сигналов dG и dGV) определяет задержку отраженного

сигнала по отношению к зондирующему, т.е. эта разность содержит информацию о

дальности до цели. При подаче управляющего сигнала dx1 = 1

счетчик переключается с модуля M0 на M0 – 1

или M0 + 1 в зависимости от значения другого управляющего

сигнала x2, что приводит к появлению переноса P4

на один такт раньше или позже, чем при модуле пересчета M0.

Чем выше частота f0 тактового сигнала, тем меньше

дискретность квантования фазы (дальности до цели) и тем выше качество

имитатора. Задачей курсовой работы является проектирование имитатора сигналов,

параметры которых задаются нажатием клавиш клавиатуры имитатора. Ввод в

микроЭВМ кода нажатой клавиши производится программным методом с квитированием

или по прерыванию. По коду клавиши идентифицируется ее назначение и

производится соответствующее управление работой счетчиков, обеспечивающих

заданные параметры сигналов G и GV.

временных положений сигналов dG и dGV) определяет задержку отраженного

сигнала по отношению к зондирующему, т.е. эта разность содержит информацию о

дальности до цели. При подаче управляющего сигнала dx1 = 1

счетчик переключается с модуля M0 на M0 – 1

или M0 + 1 в зависимости от значения другого управляющего

сигнала x2, что приводит к появлению переноса P4

на один такт раньше или позже, чем при модуле пересчета M0.

Чем выше частота f0 тактового сигнала, тем меньше

дискретность квантования фазы (дальности до цели) и тем выше качество

имитатора. Задачей курсовой работы является проектирование имитатора сигналов,

параметры которых задаются нажатием клавиш клавиатуры имитатора. Ввод в

микроЭВМ кода нажатой клавиши производится программным методом с квитированием

или по прерыванию. По коду клавиши идентифицируется ее назначение и

производится соответствующее управление работой счетчиков, обеспечивающих

заданные параметры сигналов G и GV.

Схема процессорного блока изображена на рисунке 3 и выполнена с использованием макроэлементов (отдельно макроэлементы представлены на рисунке 4):

74373b – регистр младшего байта адреса,

74244b – буфер старшего байта адреса, lpm_bustri – приемопередатчик системной шины данных, 74157 –

дешифратор системных сигналов управления, вырабатывающий из сигнала ![]() (Read) чтения внешнего устройства I/O или

памяти сигналы

(Read) чтения внешнего устройства I/O или

памяти сигналы ![]() (MemoryRead) – чтение данных из памяти или

(MemoryRead) – чтение данных из памяти или ![]() (I/O Read) – чтение внешнего устройства, а из

сигнала

(I/O Read) – чтение внешнего устройства, а из

сигнала ![]() (Write) записи данных в память или I/O

сигналы

(Write) записи данных в память или I/O

сигналы ![]() (MemoryWrite) – запись данных в память или

(MemoryWrite) – запись данных в память или ![]() (I/O Write) – запись во внешнее устройство в

зависимости от значения сигнала

(I/O Write) – запись во внешнее устройство в

зависимости от значения сигнала ![]() (IO/Memory), указывающего на обращение CPU к

внешнему устройству (

(IO/Memory), указывающего на обращение CPU к

внешнему устройству (![]() ) или к памяти (

) или к памяти (![]() ).

).

A15–8 (AddressBus) – старший байт адреса памяти;

AD7–0 (MultiplexedAddress/DataBus) – мультиплексная шина адреса-данных (в первом такте машинного цикла выдается младший байт адреса A7–0 памяти или адрес внешнего устройства, а в течение второго и третьего тактов машинного цикла – байт данных D7–0);

ALE (AddressLatchEnable) – сигнал фиксации младшего байта адреса A7–0 во внешнем регистре (ALE = 1 в первом такте текущего машинного цикла);

S1, S0 (Status) – сигналы состояния CPU,

указывающие совместно с сигналом ![]() тип операции, которую он будет

выполнять в текущем машинном цикле (в частности, S1 = S0

= 0 – режим останова CPU);

тип операции, которую он будет

выполнять в текущем машинном цикле (в частности, S1 = S0

= 0 – режим останова CPU);

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.