Программа выполнения лабораторной работы 1

в САПР Active-HDL7.1

Цель работы - научиться работать с САПР электронной аппаратуры Active-HDL 7.1:

· рисовать функциональные схемы цифровой аппаратуры в графическом редакторе BlockDiagramEditor;

· проектировать собственные логические элементы и триггеры;

· задавать внешние воздействия в редакторе временных диаграмм WaveformEditor;

· моделировать выполненный проект;

· анализировать результаты моделирования и измерять временные интервалы.

Перед началом работы создайте свою папку, например Lab_AHDL, в которой будут сохраняться все результаты выполненных заданий.

ЗАДАНИЕ 1. Создание проекта с помощью графического редактора BlockDiagramEditor. Ориентировочное время выполнения данного задания – 60 мин. (1,5 балла).

1.1. Запустите интегрированную среду проектирования Active-HDL 7.1, создайте в ней рабочее пространство Workspace, например Lab_AHDL, а в нём проект, например Lab1.

1.2. Активизируйте закладку designflowmanager (управление

маршрутом проектирования) и щёлкните по иконке  - вызов схемного редактора.

- вызов схемного редактора.

1.3. Появится диалоговая панель мастера NewSourceFileWizard. Выберите язык VHDL (установлен по умолчанию). Укажите имя исходного файла, в котором будет храниться создаваемая вами схема, например count5_BDE (суммирующий счётчик по модулю 5) и задайте входные C, R и выходные Q2, Q1, Q0 порты. Откроется новая закладка с рабочей областью BDE – редактора, на которой ничего нет кроме указанных вами портов.

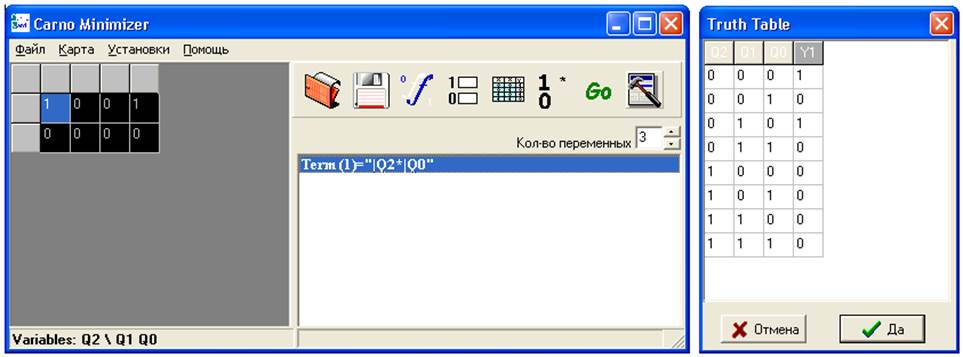

1.4. Если вариант задания не содержит готовую схему, то её придётся синтезировать на картах Карно или с помощью программы CarnoMinimizer(рис.1).

1.5. По умолчанию к схемному редактору подключена только одна встроенная библиотека символов Built-insymbols, в которой нет триггеров. Поэтому придётся добавить ещё какую-нибудь системную библиотеку элементов, например, cypress или xc9500. Можно выбрать и любую другую, где имеются модели триггеров. Но их работу желательно проверить.

Для подключения новой библиотеки щёлкните по иконке ![]() , чтобы вызвать «ящик с

символами». Откроется окно SymbolsToolbox.

Правой кнопкой мыши вызовите контекстное меню и исполните команду SelectLibraries. На диалоговой панели Libraries установите флажок на строке Cypressили присоедините

библиотеку xc9500 (она

находится в разделе XILINX).

, чтобы вызвать «ящик с

символами». Откроется окно SymbolsToolbox.

Правой кнопкой мыши вызовите контекстное меню и исполните команду SelectLibraries. На диалоговой панели Libraries установите флажок на строке Cypressили присоедините

библиотеку xc9500 (она

находится в разделе XILINX).

Рис.1. Синтез счётчика по модулю 5 с помощью программы CarnoMinimizer

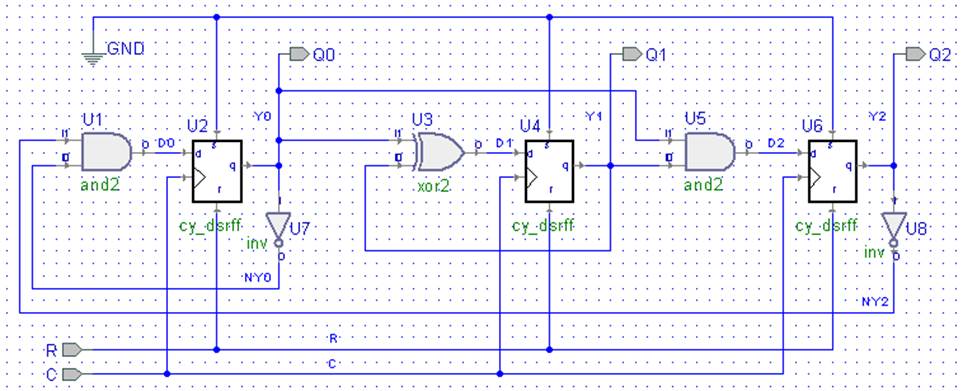

1.6. Используя логические элементы из встроенной библиотеки и триггеры из присоединённой библиотеки, нарисуйте схему, как показано на рис.2.

1.7. Откомпилируйте созданный файл (пиктограмма ![]() ) и устраните возможные ошибки.

) и устраните возможные ошибки.

1.8. Активизируйте редактор временных диаграмм WaveformEditor (кнопка

![]() ), сформируйте список

сигналов для наблюдения и задайте для входных сигналов C и Rвременные

диаграммы.

), сформируйте список

сигналов для наблюдения и задайте для входных сигналов C и Rвременные

диаграммы.

1.6. Промоделируйте свой проект на заданном наборе внешних воздействий и добейтесь правильной работы своей схемы. Результаты моделирования сохраните в волновом файле, например count5_BDE.awf.

Рис.2. Схема двоичного суммирующего счётчика по модулю

5 на элементах из

встроенной и системной библиотек

ЗАДАНИЕ 2. Проектирование логических элементов и триггеров в САПР Active-HDL 7.1. Создание схемного описания проекта на «самодельных» элементах. Ориентировочное время выполнения задания – 60 мин. (1,5 балла).

2.1. Вновь активизируйте закладку designflow и щёлкните по иконке  - вызов текстового редактора HDLEditor. Выберите язык проектирования VHDL

(он задаётся по умолчанию).

- вызов текстового редактора HDLEditor. Выберите язык проектирования VHDL

(он задаётся по умолчанию).

2.2. С помощью мастераNewSourceFileWizard укажите имя исходного файла, где будет храниться поведенческая модель создаваемого вами логического элемента, например and2_my. Введите входные и выходные порты, например A, B, Y и отредактируйте автоматически созданный шаблон VHDL - модели. Это можно сделать несколькими способами:

§ вручную ввести VHDL - код, реализующий функцию элемента;

§ воспользоваться услугами языкового помощника LanguageAssistant(команда

с тем же именем или пиктограмма ![]() );

);

§ автоматически сгенерировать требуемый VHDL - код с помощью генератора кода IPCOREGenerator (команда с тем же названием в меню Tools).

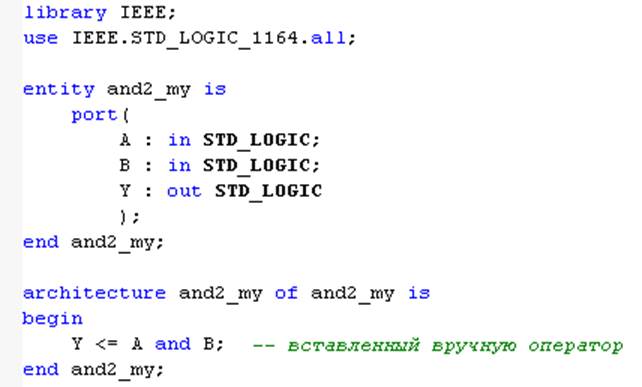

Должен получиться примерно такой код (рис.3):

Рис.3. Одна из возможных реализаций VHDL – модели логического элемента and2_my

2.3. Откомпилируйте созданный текстовый файл

(пиктограмма ![]() ) и устраните

возможные ошибки.

) и устраните

возможные ошибки.

2.4. Активизируйте редактор временных диаграмм WaveformEditor (кнопка

![]() ), сформируйте список

сигналов для наблюдения и задайте временные диаграммы для входных сигналов A и B.

), сформируйте список

сигналов для наблюдения и задайте временные диаграммы для входных сигналов A и B.

2.5. Установите модель тестируемого элемента в качестве объекта верхнего уровня (команда SetasTop-Level) и промоделируйте её на заданном наборе внешних воздействий.

2.6. Аналогичным образом создайте остальные типы элементов, используемых в вашем проекте, например nand2_my, or2_my, inv_my, xor_my, dff_my. Желательно проверить их в работе. Особенно внимательно отнеситесь к логике функционирования триггеров.

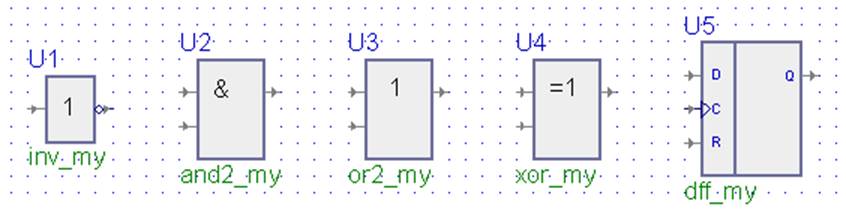

2.7. Откройте схемный редактор и поместите на экране созданные компоненты. Графические описания своих элементов рисовать не нужно. Система их генерирует автоматически при первом вызове на схему. Достаточно лишь немного отредактировать их, приблизив к требованиям отечественных стандартов (рис.4).

Рис.4. Условные графические

обозначения компонентов, приближенные

к требованиям отечественных стандартов

2.8. Нарисуйте на созданных элементах ту же самую

схему, что была спроектирована по первому заданию. С этой целью активизируйте

закладку designflowmanager (управление маршрутом проектирования) и щёлкните по

иконке  - вызов схемного

редактора.

- вызов схемного

редактора.

2.9. Появится диалоговая панель мастера NewSourceFileWizard. Выберите язык VHDL (установлен по умолчанию). Укажите имя исходного файла, в котором будет храниться создаваемая вами схема, например count5_BDE_my и задайте входные C, R и выходные Q2_my, Q1_my, Q0_my порты. Откроется новая закладка с рабочей областью BDE – редактора, на которой ничего нет кроме указанных вами портов.

Для экономии времени можно скопировать ранее созданную схему и заменить в ней элементы из встроенной и системной библиотек на свои собственные. Полученная схема должна выглядеть примерно так, как показано на рис.5.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.