Однако, в качестве основной памяти (ОП) выбраны микросхемы фирм AMD и CYPRESS - флэш-память AM28F512 и статическая память CY62256 соответственно. Это обусловлено отсутствием отечественных микросхем с необходимыми временными характеристиками и необходимой информационной емкостью.

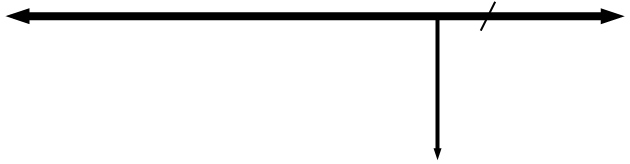

III. Обобщенная структура ядра микро ЭВМ.

Ядро микроЭВМ

|

Микропроцессор Интерфейс |

|

БС

|

AB |

|

18 |

|

DB |

|

32 |

СB |

|

3 |

|

И, DCA ROM 512kb |

|

И,DCA RAM 512Kb |

Рис. 1. Структурная схемаядра микроЭВМ.

ПУ представлены ROM и RAM. Их взаимодействие с микропроцессором происходит через системные шины. Интерфейс И памятей производит дешифрацию адреса и согласование обращений к ПЗУ, ОЗУ. Блок синхронизации управляет работой микропроцессора .

IV. Разработка структурной схемы микропроцессора.

В данной работе микропроцессор представлен как устройство, состоящее из микропрограммного устройства управления(МУУ) и операционного блока(ОБ).

Микропроцессор должен выполнять определенные команды, формат которых рассмотрен ниже.

IV. 1. Формат команд.

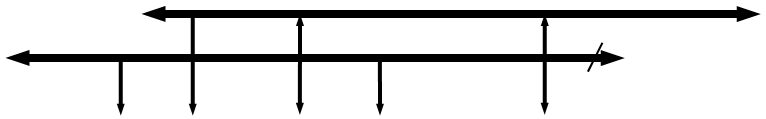

Система команд разрабатываемого устройства может включать в себя 5 различных типов команд:

1) Команда типа «регистр – регистр»

Т КОП Adr RG B Adr RG A W P

31 30 23 22 17 16 11 10 6 5 0

где:

P – 6ти разрядное поле задания позиции правой границы обрабатываемого битового поля АЛУ.

W – задает ширину битового поля АЛУ.

Adr RG A – адрес регистра – источника.

Adr RG B – адрес регистра - приемника.

КОП – код операции.

Т – бит присутствия двухсловной команды (Т=L однословная команда).

При выполнении какой-либо операции, операнды берутся из регистров, адресуемых полями Adr RG B и Adr RG A, результат операции помещается в регистр по адресу Adr RG B.

2) Команда типа «регистр – память»

Т КОП Adr RG B Adr RG mem1 W P

31 30 23 22 17 16 11 10 6 5 0

Adr mem

31 0

где: P, W, Adr RG B, КОП – аналогично п. 1)

Adr RG mem1 – адрес регистра, в котором находится адрес памяти, где и лежат данные.

Adr mem – адрес памяти, по которому находятся данные.

3) Команда типа «память – регистр»

Т КОП Adr RG mem1 Adr RG A W P

31 30 23 22 17 16 11 10 6 5 0

Adr mem

31 0

P, W, Adr RG mem1, КОП, Adr mem – аналогично п. 2)

Adr RG A – п. 1)

4) Команда типа «регистр – непосредственные данные»

Т КОП Adr RG B Adr RG A W P

31 30 23 22 17 16 11 10 6 5 0

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.