|

№ Поля |

Бит |

Наименование |

Функциональное назначение |

Блок |

Уровень активности |

|

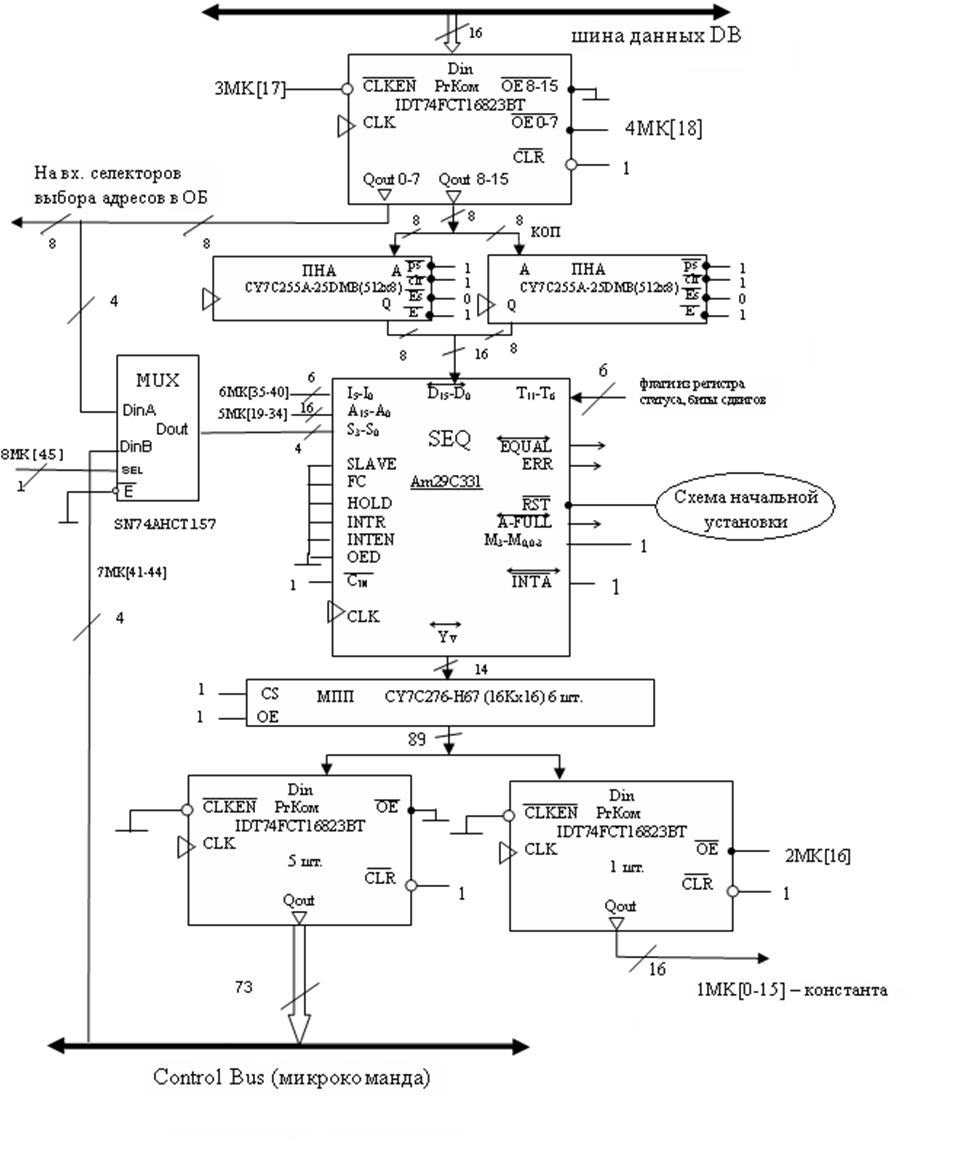

Микропрограммное устройство управления |

МУУ |

||||

|

1 |

0-15 |

Const |

Константа в операционный блок |

||

|

2 |

16 |

OE# |

Разрешение вывода константы в ОБ |

LOW |

|

|

3 |

17 |

СLKEN# |

Разрешение синхронной загрузки регистра команд |

LOW |

|

|

4 |

18 |

OE 0-7# |

Разрешение вывода адреса для РГФ |

LOW |

|

|

5 |

19-34 |

A0..A15 |

Адрес перехода секвенсора |

||

|

6 |

35-40 |

I0..I5 |

Инструкции секвенсору |

||

|

7 |

41-44 |

S0...S3 |

Выбор условий тестирования секвенсора |

||

|

8 |

45 |

Sel |

Источник выбора условия для секвенсора. 0 - условие из РгКом, 1 – из РгМк |

||

|

Основная память |

Па-мять |

||||

|

9 |

Чтение |

||||

|

10 |

Запись |

||||

|

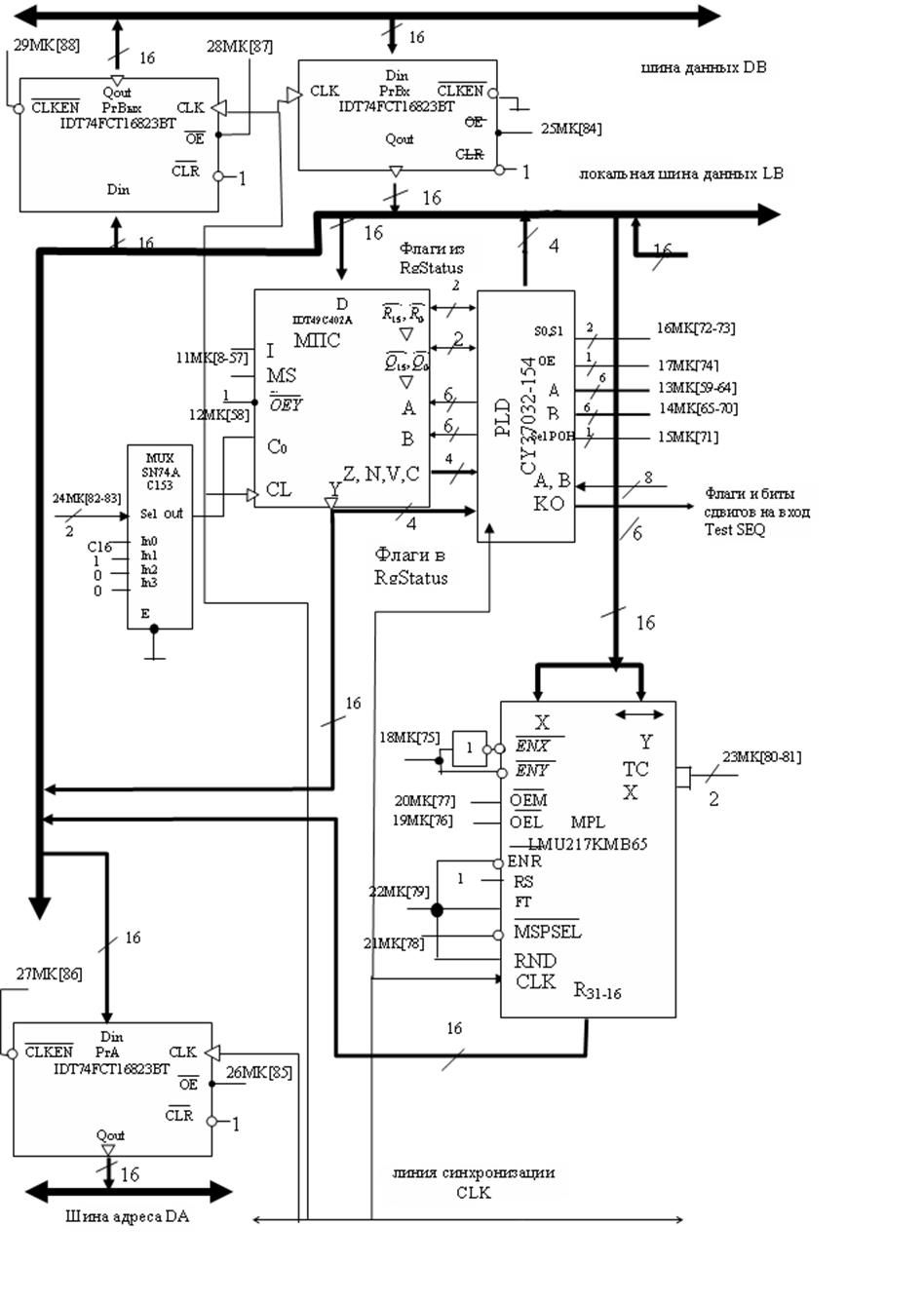

МПС IDT49C402A |

ОБ |

||||

|

11 |

48-57 |

I0-I9 |

Инструкции управления МПС |

||

|

12 |

58 |

OEY# |

Разрешение вывода в Y шину |

LOW |

|

|

Блок статусного регистра, логики сдвигов и выбор адресов РГФ (PLD CY37032-154) |

|||||

|

13 |

59-64 |

Sel A0-A5 |

Адрес чтения из РОН A |

||

|

14 |

65-70 |

Sel B0-B5 |

Адрес чтения/записи из РОН B |

||

|

15 |

71 |

Sel РОН |

Управление выбором адреса для РОН 0 – адрес берется из РгК, 1 – адрес из РгМк |

||

|

16 |

72,73 |

S0, S1 |

Тип сдвига |

||

|

17 |

74 |

OE |

Разрешение вывода слова состояния на локальную шину |

HIGH |

|

|

Параллельный умножитель LMU217KMB65 |

|||||

|

18 |

75 |

ENX#, ENY# |

Управление загрузкой: LOW – загрузка RGY, HIGH – загрузка RGX |

||

|

19 |

76 |

OEL# |

Разрешение вывода в R31-16 младшей части произведения |

LOW |

|

|

20 |

77 |

OEM# |

Разрешение вывода в R31-16 старшей части произведения |

LOW |

|

|

21 |

78 |

MSPSEL# |

LOW разрешает выдавать на выход старшие 16 разрядов произведения из регистра результата, а HIGH - младшую часть произведения. |

||

|

22 |

79 |

RND |

Управление режимом округления |

HIGH |

|

|

23 |

80,81 |

TCX, TCY |

Входы задания формата операндов (знаковые - HIGH/беззнаковые - LOW) |

||

|

Мультиплексор SN74AS153 (на входе С0) |

|||||

|

24 |

82,83 |

Sel0, Sel1 |

Управление выбором флага вх. пер. С0. 00: С0=С16, 01: С0=1, 10: С0=0. |

||

|

Регистр входных данных IDT74FCT16374ET |

|||||

|

25 |

84 |

OE# |

Разрешение вывода |

LOW |

|

|

Регистр адреса IDT74FCT16374ET |

|||||

|

26 |

85 |

OE# |

Разрешение вывода |

LOW |

|

|

27 |

86 |

CLKEN# |

Разрешение синхронной загрузки регистра |

LOW |

|

|

Регистр выходных данных IDT74FCT16374ET |

|||||

|

28 |

87 |

OE# |

Разрешение вывода |

LOW |

|

|

29 |

88 |

CLKEN# |

Разрешение синхронной загрузки регистра |

LOW |

|

Итого: 29 команд, 89 бит

ПРИМЕЧАНИЕ. Обозначение на схемах XXMK[K1-K2] означает, что это поле №XX микрокоманды и биты с K1 по K2 включительно.

В результате выполнения курсовой работы был разработан прототип ядра микроЭВМ, состоящий из микропроцессора(в состав которого входит ОБ и МУУ), основной памяти(оперативной SRAM и постоянной EPROM), блока синхронизации и схемы начальной установки процессора, а также изучены основные принципы и проблемы, возникающие при проектировании аппаратных средств вычислительной техники. Было выполнено большинство требований, предъявляемых к разработке ядра микроЭВМ.

В общем, хочется отметить, что работа оказала большую помощь в приобретении практических знаний по разработке устройств микроЭВМ.

1. Соболев В.И. Схемотехника. Руководство к курсовой работе: – Новосибирск: НГТУ, 1997.

2. Угрюмов Е.П. Цифровая схемотехника.: Учебное пособие для вузов: - 2-е издание, переработанное и дополненное - СПб: БХВ - Петербург, 2005. - 800с.

3. Угрюмов Е.П Проектирование элементов и узлов ЭВМ: Учебное. пособие для вузов. - М.: Высш.шк., 1987. - 318 с.

4. Интернет-ресурс www.cypress.com

5. Интернет-ресурс www.idt.com

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.