Из таблицы очевидно, что минимальная длительность цикла основной памяти составляет 68.5 нс.

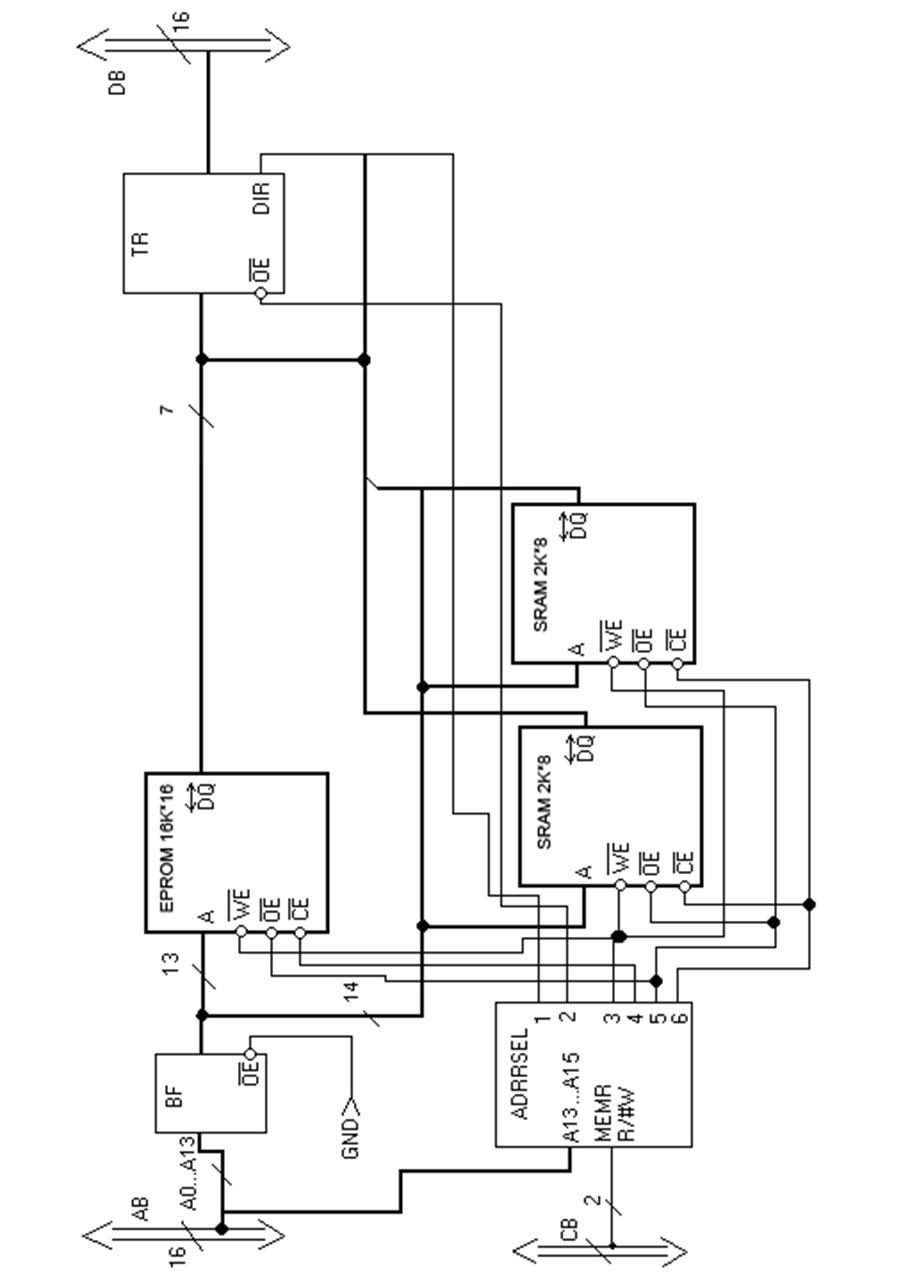

рис. 4. Функциональная схема модуля памяти

Максимальная длительность цикла ОБ – 80 нс., МУУ – 78,5 нс., памяти – 68,5 нс. Итоговая длительность цикла ядра определяется по длительности цикла МУУ. Но из-за превышающей её длительности цикла ОБ установим длительность цикла ядра в 80 нс. Форма синхросигнала выбрана с расчетом на длительность положительного и отрицательного уровня при прохождении данных через статусный регистр, регистр адреса, регистр команд и показана на рис. 3:

|

|

При включении питания необходимо выполнить сброс секвенсора микрокоманд (установить адрес первой микрокоманды по нулевому адресу) путём подачи сигнала RES# на вход сброса RST# секвенсора.

Схема начальной установки выполнена с применением микросхемы MC34064, фирмы MOTOROLA. Микросхема MC34064 это специализированный для микропроцессорных систем контроллер предустановки, применяемый для выработки асинхронного сигнала RSTASYNC#. Производитель не рекомендует делать время начальной установки схемы менее 500нс.

Возьмем R = 16

кОм, С = 100 пФ. Емкостью триггеров можно пренебречь. Тогда имеем: tRSTASYNC#=16*103*100*10-12*ln((5-1.4)/5)=526 нс. Полученное значение нам подходит.

Возьмем R = 16

кОм, С = 100 пФ. Емкостью триггеров можно пренебречь. Тогда имеем: tRSTASYNC#=16*103*100*10-12*ln((5-1.4)/5)=526 нс. Полученное значение нам подходит.

Для нормальной работы микросхемы секвенсора AM29C331 необходим синхронный сигнал сброса. Поэтому для преобразования асинхронного сброса в синхронный используются 2 D-триггера: синхронный сброс повторяет асинхронный, но переключается не в любой момент времени, а только по фронту синхросигнала, подаваемый на первый триггер и сигналу сброса R#, подаваемый на второй триггер. Временные диаграммы (рис. 3) поясняют принцип работы схемы несколько подробно. Сигнал сброса получается «хорошим», если время переключения триггеров малое.

|

Рис. 6. Схема начальной установки

|

|

|

|

|

|||||||||||

|

|

||||||||||||||

|

|

||||||||||||||

|

|

||||||||||||||

|

|

||||||||||||||

|

|

||||||||||||||

Рис. 7. Временные диаграммы работы схемы

Блок синхронизации выбирается на основании длительности синхросигнала: период TCLK должен быть не меньше двух времен цикла ОБ, т.е. TCLK >= 2*80=160 нс. Во всей схеме синхронизация однофазная.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.