Новосибирский Государственный Технический Университет

Кафедра Вычислительной Техники

|

РАСЧЕТНО-ГРАФИЧЕСКАЯ работа

По дисциплине «Схемотехника»

«проектирование модулей памяти»

Выполнила: Проверила:

Ст. Бажок И.С. Соболев В.И.

Гр. АМ-211

АВТФ

Новосибирск 2004

Оглавление

1. Техническое задание к работе. 3

2. Выбор элементной базы.. 3

3. Построение модуля памяти. 4

4. Расчет создаваемой нагрузки. 7

5. Выбор интерфейсных элементов. 8

6. Расчет времени цикла. 9

7.Выводы. 11

8. Список используемой литературы: 12

Разработать комбинированный модуль памяти, состоящий из модуля SRAM (статической оперативной) объёмом 2 Кб, разрядностью слова 16 бит и модуля EPROM объёмом 32 Кб аналогичной разрядности слова. Время цикла не более 70нс. Обеспечить электрический интерфейс ТТЛ. Обеспечить трехшинный системный интерфейс.

Подсчитаем информационную организацию создаваемого модуля:

SRAM – (1K*16) бит

EPROM – (16K*16) бит

Исходя из требований к информационной организации и времени цикла выберем следующие типономиналы:

SRAM серии CY7C148-35, его характеристики:

· Информационная организация (1К x 4)

· Максимальное время доступа – 35нс.

· Напряжение питания – 5В±10%

· Схемотехнология - КМОП

Временные характеристики и диаграммы для выбранных ИМС памяти представлены в приложении1.

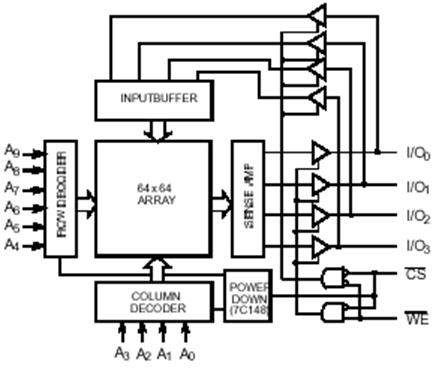

Ниже на рис. 1 представлена функциональная схема ИМС.

Рис. 1. Схема ИМС памяти CY7C148-35

Таблица 1. Назначение входов управления БИС (SRAM)

|

CS# |

WE# |

Производимая операция |

|

L |

L |

Запись |

|

L |

H |

Чтение |

|

H |

Х |

Z |

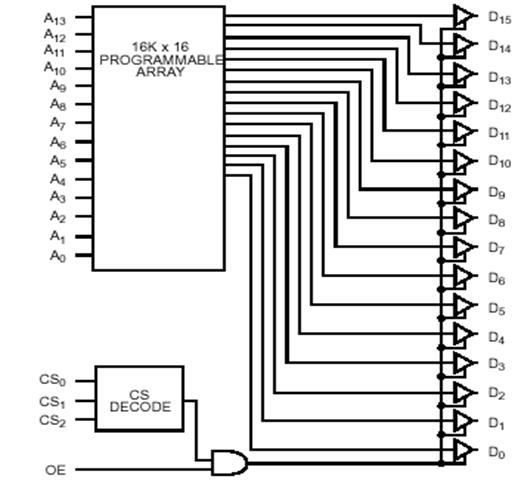

EPROM серии CY7C276-35, его характеристики:

· Информационная организация (16К x 16)

· Максимальное время доступа – 35 нс.

· Напряжение питания – 5В±10%

· Схемотехнология - КМОП

Рис. 2. Схема ИМС памяти CY7C276-35

Таблица 2. Назначение входов управления БИС (EPROM)

|

CS0 – CS2 |

OE |

Состояние |

|

H |

H |

Чтение |

|

L |

Х |

Z |

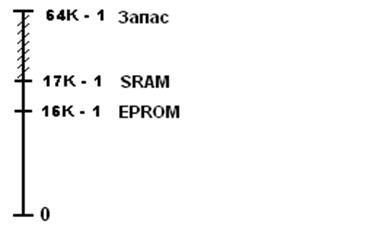

Необходимо рассчитать, сколько ИМС требуется для организации накопителя. Исходя из требований технического задания и выбранных типономиналов, делаем вывод, что требуется 4 ИМС SRAM (для увеличения разрядности хранимого слова) и одна ИМС EPROM. Составим карту памяти для проектируемого устройства:

Рис. 3 Карта памяти

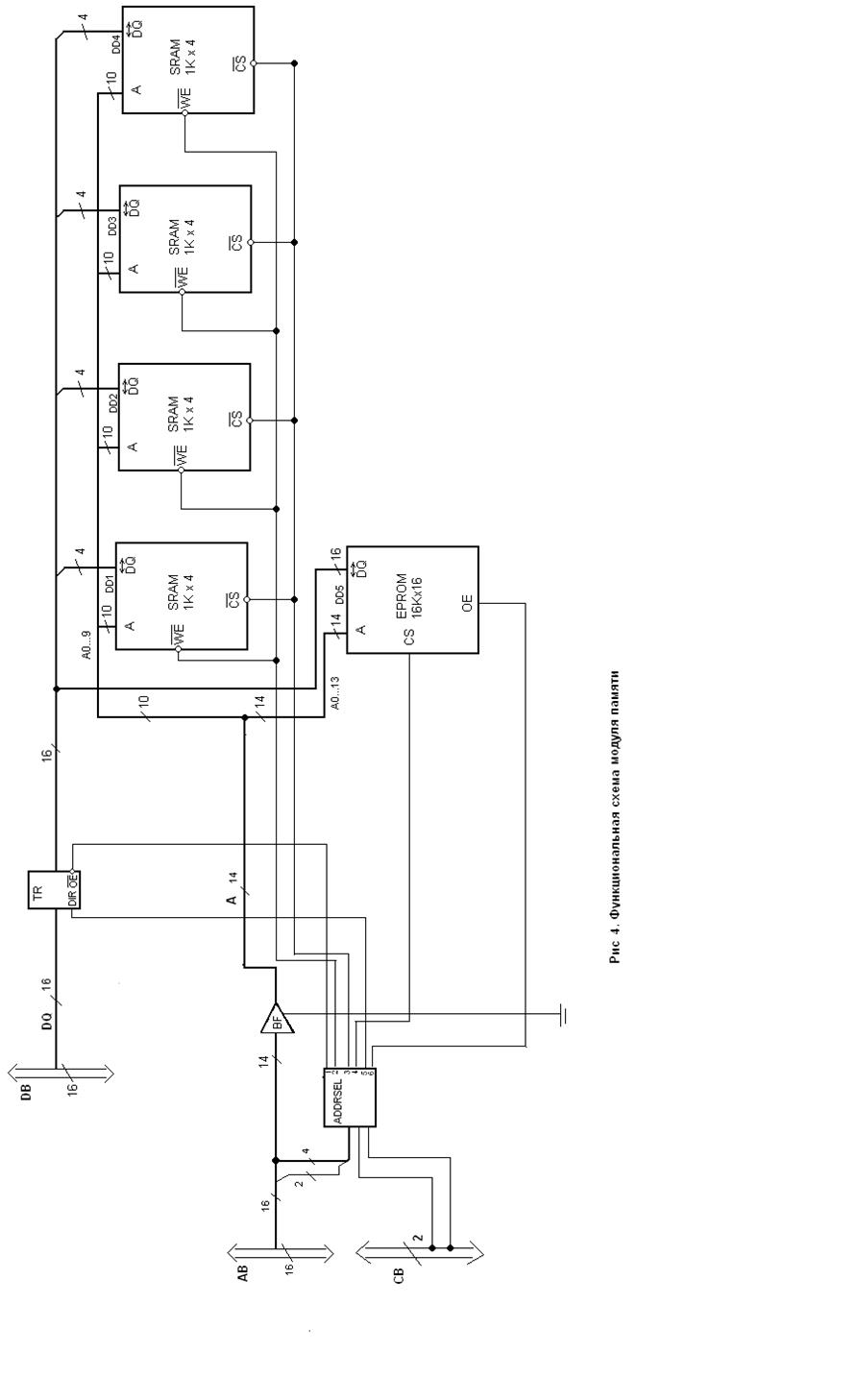

Ниже, на рис.4 представлена функциональная схема модуля памяти.

Таблица 5. Элементы функциональной схемы и их назначение.

|

Обозначение |

Наименование |

Назначение |

|

DD1…4 |

Модуль SRAM памяти серии CY7C148-35 |

Накопитель информации |

|

DD5 |

Модуль EPROM памяти серии CY7C276-35 |

Накопитель информации |

|

TR |

Трансивер, серия CY74FCT16245T |

Прием и передача 16 битов данных |

|

BF |

Буфер, серия CY74FCT16244T |

Передача 14 битов адреса. |

|

ADDRSEL |

Адресный селектор построен на программируемой логике, серияATF1502ASL |

Проверка к нашему ли модулю обращение, формирование управляющих сигналов |

Пояснения к схеме модуля памяти:

АВ – магистральная шина адреса

DВ – магистральная тридцатидвухразрядная шина данных

СВ – шина управления, содержит два сигнала: MEMR, #W/R

DQ – двунаправленная внутренняя шина данных (DQ0…15)

A – внутренняя шина адреса (A0…13)

#W/R – сигнал управления чтением/записью

MEMR – сигнал активации памяти, высокий уровень разрешает работу памяти, низкий соответствует её пассивизации.

CS# – вход выбора кристалла (для модуля SRAM)

WE# – вход разрешения записи (для модуля SRAM)

CS – вход выбора кристалла (для модуля EPROM) (3 объединено в один)

#OE – вход разрешения вывода (для модуля EPROM)

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.