Буфер CY74FCT16244T состоит из четырех 4-битных буферов, каждый из которых имеет свой OE#, мы используем все 16 бит буфера, поэтому необходимо разрешающие входы OE# соединить параллельно. Буфер BF2 используется не только для буферизации сигналов линии адреса, но и для добавления задержки в путь распространения сигнала #W/R.

Таблица 4.Функциональная таблица буфера CY74FCT16244T

|

OE# |

AВ |

А(выходы) |

|

L |

L |

L |

|

L |

H |

H |

|

H |

X |

Z |

Таблица 5. Функциональная таблица трансивера CY74FCT16245T

|

OE# |

DIR |

Состояние трансивера |

|

L |

L |

Вывод данных |

|

L |

H |

Ввод данных |

|

H |

X |

Z |

Таблица 6. Временные характеристики для чтения из SRAM.

|

Характеристика |

Описание |

Значение, нс. |

|

t1 |

Время формирования сигналов #W/R, #CS Тракт: CB->ADDRSEL |

7.5 |

|

taa |

Время выборки адреса. |

35 |

|

tTR |

Время задержки данных трансивером |

7 |

|

tBF |

Задержка буфера |

6,5 |

|

tц |

Время цикла чтения |

68 |

|

tHZ |

Время переключения сигнала CS# в высокое состояние до окончания данных. |

10 |

|

tOH |

15 |

Временная диаграмма для чтения из SRAM на рис. 5.

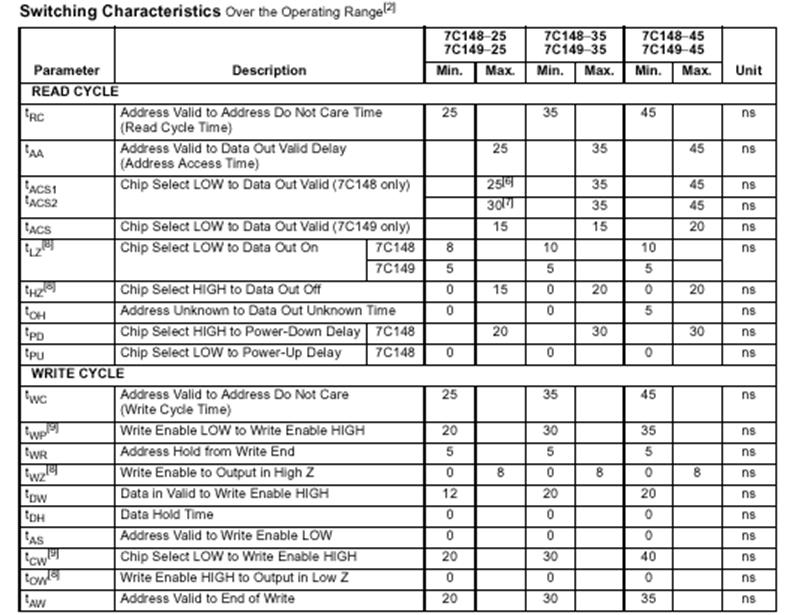

Таблица 7. Временные характеристики для записи в SRAM.

|

Характеристика |

Описание |

Значение, нс. |

|

t1 |

Время формирования сигналов #W/R, #CS Тракт: CB->ADDRSEL |

7.5 |

|

tDIR+ tTR |

Задержка на установку направления в трансивере и задержка данных трансивером |

16,5 |

|

tBF |

Время задержки буфера |

6,5 |

|

tDW |

Время установки данных |

20 (min) |

|

tWA |

Время удержания адреса |

5(min) |

|

tц |

Время цикла записи: |

69 |

Временная диаграмма для записи в SRAM на рис. 6.

Таблица 8. Временные характеристики для чтения из EPROM.

|

Характеристика |

Описание |

Значение, нс. |

|

t1 |

Время формирования сигналов #W/R, #CS Тракт: CB->ADDRSEL |

7,5 |

|

taa |

Время выборки адреса. |

35 |

|

tTR |

Время задержки данных трансивером |

7 (max) |

|

tBF |

Время задержки буфера |

6,5 |

|

tц |

Время цикла чтения (от подачи управляющих сигналов до появления данных на внешней шине): tц = t2 + t3 + tTR Тракт: R/W# -> NOT -> NOT ->BF2 -> NOT->DIR |

67 |

|

tOEZ |

Время отключения OE до окончания данных |

15 |

|

tCSOZ |

Время отключения CS до окончания данных |

18 |

Временная диаграмма для чтения из EPROM на рис. 7.

В итоге работы был построен модуль памяти, который соответствует всем выдвинутым в техническом задании требованиям как:

· Информационная емкость и организация – (17К х 16)бит

· Время цикла

· Электрический интерфейс – ТТЛ

· Системный интерфейс - трехшинный

В процессе проектирования модуля памяти были изучены соответствующие разделы учебных пособий, посвященные вопросам проектирования узлов ЭВМ, такие как учебное пособие Угрюмова Е.П. Были освоены основные методы построения модулей памяти и простейших способов управления ими. Были получены навыки работы с технической документацией. В дальнейшем время работы над подобными проектами будет существенно меньше, в связи с приобретенными навыками поиска документации по различным устройствам.

1. Угрюмов Е. П. Проектирование элементов и узлов ЭВМ.: М. изд. Высшая школа 1987г.

2. Сайты зарубежных компаний:

www.cypress.com

www.ti.com

www.atmel.com

Приложение 1

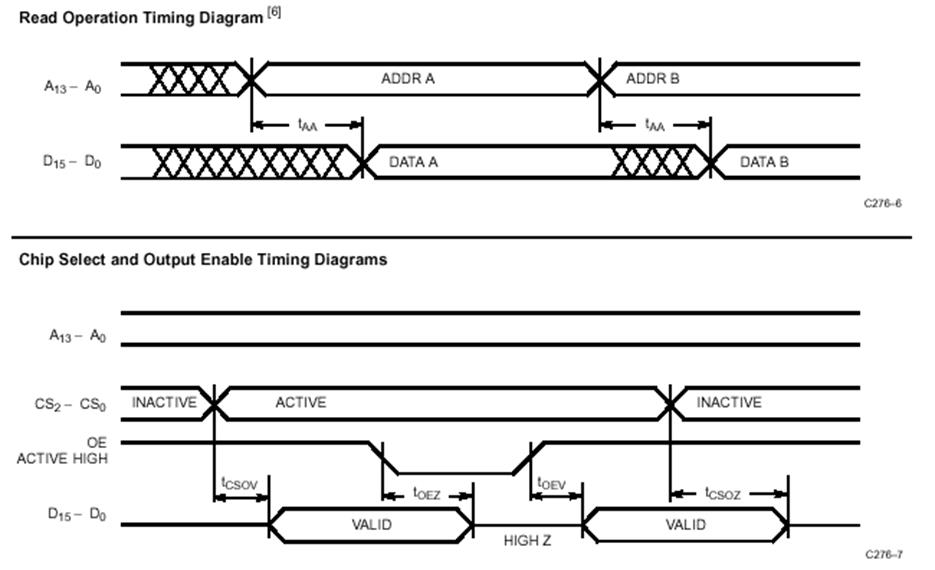

Рис.8 Временные диаграммы чтения МС CY7C276

Рис.9 Временные параметры МС CY7C276

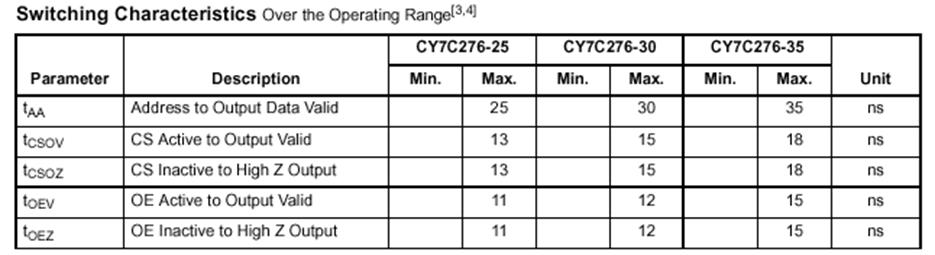

Рис. 10 Временные диаграммы чтения МС CY7C148

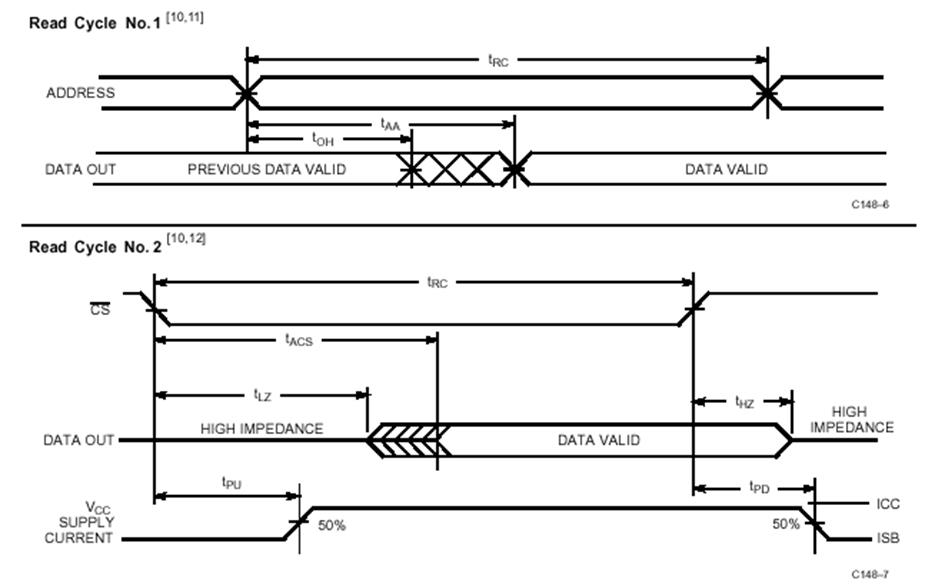

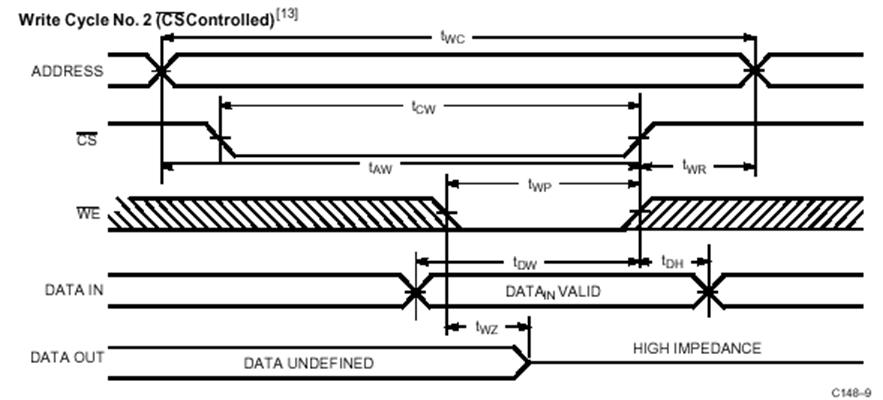

Рис. 11 Временные диаграммы

(1) записи МС CY7C148

Рис. 11 Временные диаграммы

(1) записи МС CY7C148

Рис. 12 Временные диаграммы (2) записи МС CY7C148

Рис. 13 Временные характеристики МС CY7C148

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.