Новосибирский Государственный

Технический Университет

Кафедра ВТ

Курсовая работа по схемотехнике

«Проектирование модуля памяти»

Студент: Перов Е.Е.

Группа: АМ-211

Преподаватель: Соболев В.И.

Новосибирск, 2004

Задание

Flash File 16 MB, 32 bit, 100 ns

Разработка модуля памяти

Микросхема должна соответствовать заданию по быстродействию и информационной емкости. Выбрана микросхема производства фирмы AMD AM29F032B 32 Megabit (4M * 8bit).

Информационная организация: 16 MB, 32 bit => (4M * 32 bit)

Далее определяем необходимое количество МС (Qбис) и количество страниц (Qстр) памяти.

Qбис

=  , где

, где ![]() - объем

памяти модуля;

- объем

памяти модуля;

![]() - объем

памяти выбранной МС;

- объем

памяти выбранной МС;

![]() -

разрядность модуля памяти;

-

разрядность модуля памяти;

![]() -

разрядность выбранной МС;

-

разрядность выбранной МС;

Qбис

=

Qстр

=  , где

, где ![]() и

и ![]() - разрядности модуля памяти и выбранной МС.

- разрядности модуля памяти и выбранной МС.

Qстр

=

Для адресации модуля памяти с системной шины адреса используются 23 младших разряда адресной шины.

Так как у нас только одна физическая страница, то DC активации не требуется.

Коэффициент объединения на линии адреса:

Kоб.А

=  , где

, где ![]() - объем

памяти модуля;

- объем

памяти модуля;

![]() - объем

памяти выбранной МС;

- объем

памяти выбранной МС;

![]() -

разрядность модуля памяти;

-

разрядность модуля памяти;

![]() -

разрядность выбранной МС;

-

разрядность выбранной МС;

Kоб.А = 4

Коэффициент объединения по входам разрешения чтения/записи:

Kоб.R/W =

Kоб.R/W = 4

Коэффициент объединения на шине данных:

Kоб.DQ =  ,

где

,

где ![]() - объем памяти модуля;

- объем памяти модуля;

![]() - объем

памяти выбранной МС;

- объем

памяти выбранной МС;

Kоб.DQ = 1

Нагрузка на линии адреса:

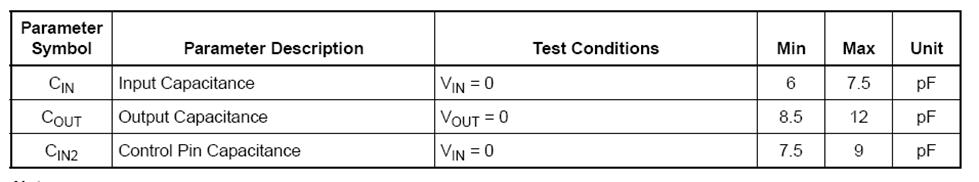

Снагр.ЛА = Сin бис * Kоб.А + Смонт, где Сin бис – max емкостная нагрузка по

входам, Смонт – емкостная нагрузка монтажа (20 пФ).

Снагр.ЛА = 7.5 * 4 + 20 = 50 пФ

Нагрузка на шине данных:

Снагр.DQ = Сout бис * (Kоб.DQ – 1) + Смонт, где Сout бис – max емкостная

нагрузка по входам МС, Смонт – емкостная нагрузка монтажа (20 пФ).

Снагр.DQ = 20 пФ

Согласно стандарту ТТЛ, пиковое значение ёмкостной нагрузки не должно превышать 10 пФ. Сравнивая это значение с полученными фактическими значениями ёмкостной нагрузки по шинам адреса, данных и управления, можем сделать вывод, что как для шины данных, так и для линий адреса и управления буферизация необходима.

Для шины адреса: 54/74FCT16244T 16 bit Buffer/Line Driver.

Для адресации памяти внутри выбранных МС используем 22-разрядную шину.

Для шины данных: 74FCT162H245T BiDirectional Transceiver.

Так как шина данных 32-разрядная, то используем 2 буфера выбранного

типономинала.

Для буферизации управляющих сигналов (OE#, WE#) используем два последовательно соединенных инвертора 54AC0412A.

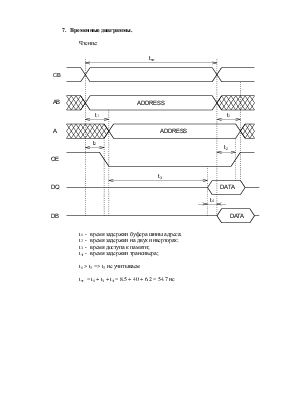

Чтение:

t1 - время задержки буфера шины адреса;

t2 - время задержки на двух инверторах;

t3 - время доступа к памяти;

t4 - время задержки трансивера;

t1 > t2 => t2 не учитываем

tчт. = t1 + t3 + t4 = 8.5 + 40 + 6.2 = 54.7 нс

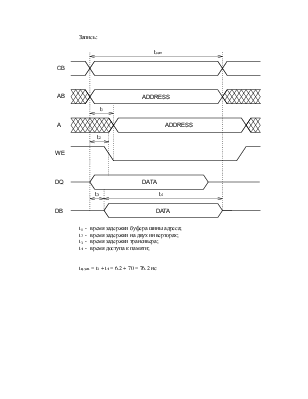

Запись:

t1 - время задержки буфера шины адреса;

t2 - время задержки на двух инверторах;

t3 - время задержки трансивера;

t4 - время доступа к памяти;

tц.зап. = t3 + t4 = 6.2 + 70 = 76.2 нс

выводы из проделанной работы.

Требования по нагрузочным и временным характеристикам выполняются.

Требования по информационной организации и емкости накопителя выполняются.

В ходе выполнения данной работы были получены новые и закреплены имеющиеся знания по дисциплине «Схемотехника». Приобретены навыки по проектированию цифровых электрических схем и в частности модуля памяти заданной информационной организации. Также была проведена большая работы по поиску технической документации. Требования технического задания и цели работы выполнены.

Приложение (характеристики используемых элементов)

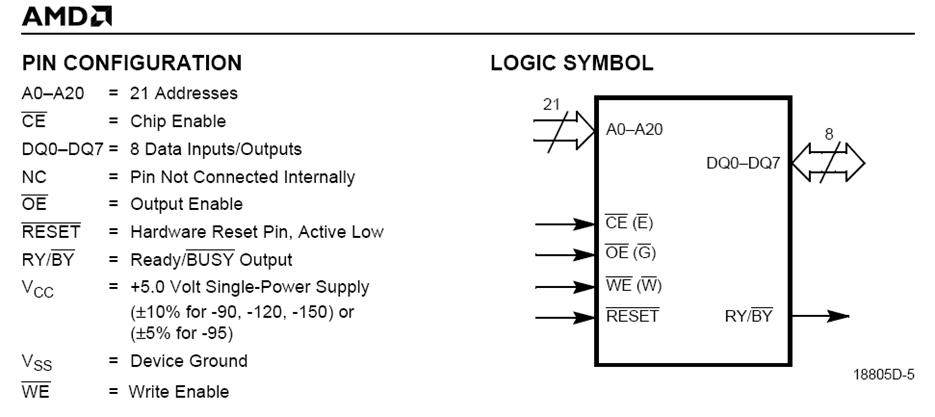

Назначение выводов, и логическое обозначение ИМС памяти:

Значения емкостей входов/выходов:

Invertor NSC 54AC04/2A

Buffered inputs

Typical Propagation Delay: 4ns at VCC = 5V, CL = 15 pF, TA = 25˚C

Fanout (Over Temperature Range)

- Standard Outputs……………………………..10 LSTTL Loads

- Bus Driver Outputs…………………………..15 LSTTL Loads

Wide Operating Temperature Range………………...-55˚C to 125˚C

Balanced Propagation Delay and Transition Times

Significant Power Reduction Compared to LSTTL Logic ICs

HC Types

- 2-V to 6-V Operation

- High Noise Immunity: NIL = 30%, NIH = 30% of VCC at VCC = 5V

HCT Types

- 4.5-V to 5.5-V Operation

- Direct LSTTL Input Logic Compatibility, VIL = 0.8V (MAX), VIH = 2V (MIN)

- CMOS Input Compatibility, I1 μA at VOL, VOH

Am29F032B

32 Megabit (4 M x 8-Bit)

CMOS 5.0 Volt-only, Uniform Sector Flash Memory

DISTINCTIVE CHARACTERISTICS

■ 5.0 V ± 10%, single power supply operation

— Minimizes system level power requirements

■ Manufactured on 0.32 µm process technology

■ High performance

— Access times as fast as 70 ns

■ Low power consumption

— 30 mA typical active read current

— 30 mA typical program/erase current

— <1 µA typical standby current (standard access

time to active mode)

■ Flexible sector architecture

— 64 uniform sectors of 64 Kbytes each

— Any combination of sectors can be erased.

— Supports full chip erase

— Group sector protection:

— A hardware method of locking sector groups to

prevent any program or erase operations within

that sector group

— Temporary Sector Group Unprotect allows code

changes in previously locked sectors

■ Embedded Algorithms

— Embedded Erase algorithm automatically

preprograms and erases the entire chip or any

combination of designated sectors

— Embedded Program algorithm automatically

writes and verifies bytes at specified addresses

■ Minimum 1,000,000 write/erase cycles

guaranteed

■ 20-year data retention at 125°C

— Reliable operation for the life of the system

■ Package options

— 40-pin TSOP

— 44-pin SO

■ Compatible with JEDEC standards

— Pinout and software compatible with

single-power-supply Flash standard

— Superior inadvertent write protection

■ Data# Polling and toggle bits

— Provides a software method of detecting program

or erase cycle completion

■ Ready/Busy output (RY/BY#)

— Provides a hardware method for detecting

program or erase cycle completion

■ Erase Suspend/Resume

— Suspends a sector erase operation to read data

from, or program data to, a non-erasing sector,

then resumes the erase operation

■ Hardware reset pin (RESET#)

— Resets internal state machine to the read mode

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.