Программа выполнения лабораторной работы 2

в САПР Active-HDL7.1

Цель работы - научиться работать с САПР электронной аппаратуры Active-HDL 7.1:

· Описывать проект в виде диаграмм состояний (графов переходов) с помощью графического редактора StateDiagramEditor;

· Вводить проект в текстовом редакторе HDLEditor на языке VHDL;

· задавать внешние воздействия в редакторе временных диаграмм WaveformEditor;

· моделировать выполненный проект;

· анализировать результаты моделирования и измерять временные интервалы.

Перед началом работы загрузите в среду проектирования Active-HDL 7.1 своё рабочее пространство, созданное на первой лабораторной работе, и создайте в нём новый проект Lab2.

ЗАДАНИЕ 1. Описание проекта в виде диаграмм состояний (графов переходов) с помощью графического редактора SDE (StateDiagramEditor).

Ориентировочное время выполнения задания – 60 мин. (1,5 балла).

1.1. Активизируйте закладку designflow manager и щёлкните по иконке  (FiniteStateMachine) - вызов редактора диаграмм состояний (StateDiagramEditor).

(FiniteStateMachine) - вызов редактора диаграмм состояний (StateDiagramEditor).

1.2. Проделайте уже известную работу с мастером NewSourceFileWizard. Укажите имя исходного файла, в котором будет храниться создаваемая вамидиаграмма, например count5_FSM_flow и задайте входные C, R и выходные Q2, Q1, Q0 порты. На вопрос «Do you want to add a clock port named ‘CLK’» ответьте «Нет».

1.3. Откроется новая закладка с рабочей областью SDE – редактора, на

которой видны заданные вами порты. Дважды щёлкните на графическом изображении

порта C и установите флажок Clock,

сделав порт синхросигналом. Убедитесь, что на изображении порта появилась

соответствующая метка ![]() .

.

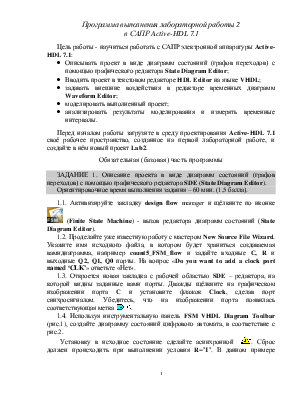

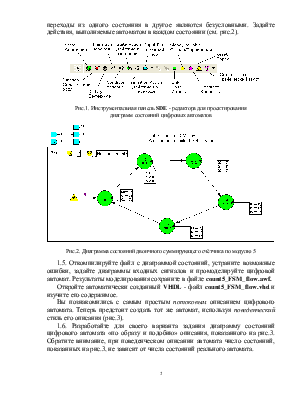

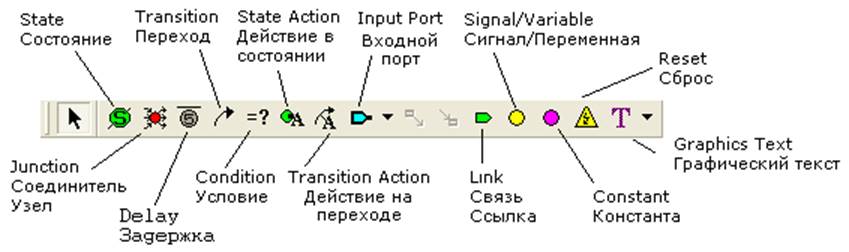

1.4. Используя инструментальную панель FSM VHDL DiagramToolbar (рис.1), создайте диаграмму состояний цифрового автомата, в соответствие с рис.2.

Установку в исходное состояние сделайте асинхронной ![]() . Сброс должен происходить при

выполнении условия R=’1’. В

данном примере переходы из одного состояния в другое являются безусловными.

Задайте действия, выполняемые автоматом в каждом состоянии (см. рис.2).

. Сброс должен происходить при

выполнении условия R=’1’. В

данном примере переходы из одного состояния в другое являются безусловными.

Задайте действия, выполняемые автоматом в каждом состоянии (см. рис.2).

Рис.1. Инструментальная панель SDE - редактора для

проектирования

диаграмм состояний цифровых автоматов

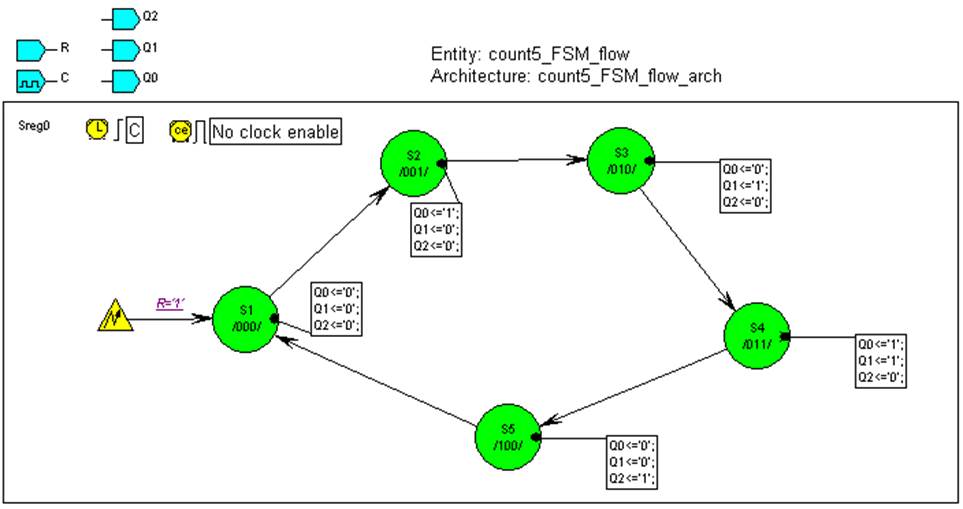

Рис.2. Диаграмма состояний двоичного суммирующего счётчика по модулю 5

1.5. Откомпилируйте файл с диаграммой состояний, устраните возможные ошибки, задайте диаграммы входных сигналов и промоделируйте цифровой автомат. Результаты моделирования сохраните в файле count5_FSM_flow.awf.

Откройте автоматически созданный VHDL - файл count5_FSM_flow.vhd и изучите его содержимое.

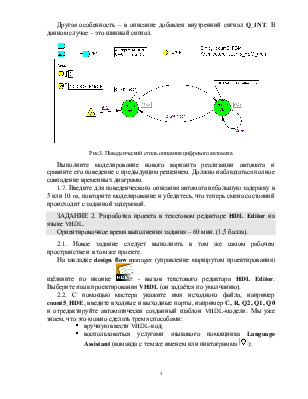

Вы познакомились с самым простым потоковым описанием цифрового автомата. Теперь предстоит создать тот же автомат, используя поведенческий стиль его описания (рис.3).

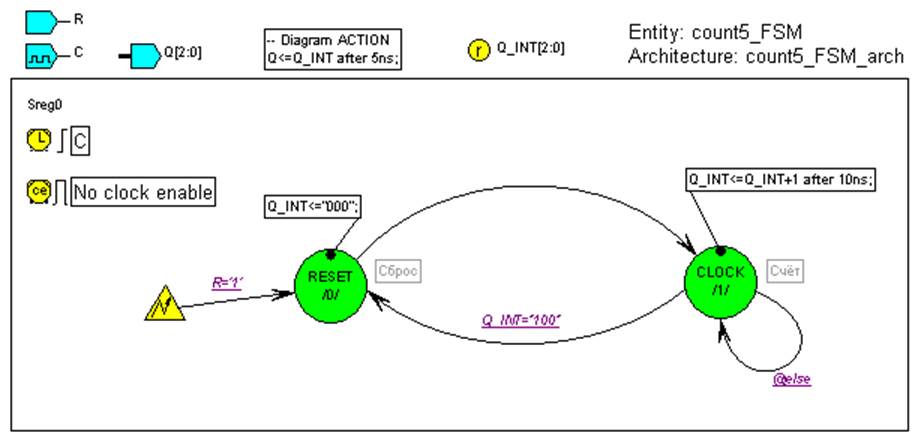

1.6. Разработайте для своего варианта задания диаграмму состояний цифрового автомата «по образу и подобию» описания, показанного на рис.3. Обратите внимание, при поведенческом описании автомата число состояний, показанных на рис.3, не зависит от числа состояний реального автомата.

Другая особенность – в описание добавлен внутренний сигнал Q_INT. В данном случае – это шинный сигнал.

Рис.3. Поведенческий стиль описания цифрового автомата

Выполните моделирование нового варианта реализации автомата и сравните его поведение с предыдущим решением. Должно наблюдаться полное совпадение временных диаграмм.

1.7. Введите для поведенческого описания автомата небольшую задержку в 5 или 10 ns, повторите моделирование и убедитесь, что теперь смена состояний происходит с заданной задержкой.

ЗАДАНИЕ 2. Разработка проекта в текстовом редакторе HDLEditor на языке VHDL.

Ориентировочное время выполнения задания – 60 мин. (1,5 балла).

2.1. Новое задание следует выполнять в том же самом рабочем пространстве и в том же проекте.

На закладке designflow manager (управление маршрутом проектирования) щёлкните по

иконке  - вызов текстового

редактора HDLEditor.

Выберите язык проектирования VHDL (он задаётся по умолчанию).

- вызов текстового

редактора HDLEditor.

Выберите язык проектирования VHDL (он задаётся по умолчанию).

2.2. С помощью мастера укажите имя исходного файла, например count5_HDE, введите входные и выходные порты, например C, R, Q2, Q1, Q0 и отредактируйте автоматически созданный шаблон VHDL-модели. Мы уже знаем, что это можно сделать тремя способами:

§ вручную ввести VHDL-код;

§ воспользоваться услугами языкового помощника LanguageAssistant(команда

с тем же именем или пиктограмма ![]() );

);

§ автоматически сгенерировать требуемый VHDL-код с помощью генератора кода IPCOREGenerator (команда с тем же названием в меню Tools).

Наиболее привлекательно выглядит третий способ. Правда не все варианты заданий он поддерживает. Настроив IPCORE генератор на конкретный цифровой узел, получим следующий код (рис.4):

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.std_logic_unsigned.all;

entity count5_HDE is

port (

C : in std_logic;

R : in std_logic;

Q0 : out std_logic;

Q1 : out std_logic;

Q2 : out std_logic

);

end entity;

--}} End of automatically maintained section

architecture count5_HDE of count5_HDE is

signal TEMP_Q : std_logic_vector(2 downto 0);

begin

process(C, R)

begin

if R = '1' then

TEMP_Q <= (others => '0');

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.