Программа выполнения лабораторной работы 4

в САПР DesignLab 8

Цель работы - научиться проектировать DSL-модели цифровых элементов и узлов:

· на основе структурного описания объекта;

· на основе функционального (поведенческого) описания объекта;

· на основе потокового представления объекта.

Перед началом работы создайте свою папку, например LAB4, в которой будут сохраняться все результаты выполненных заданий.

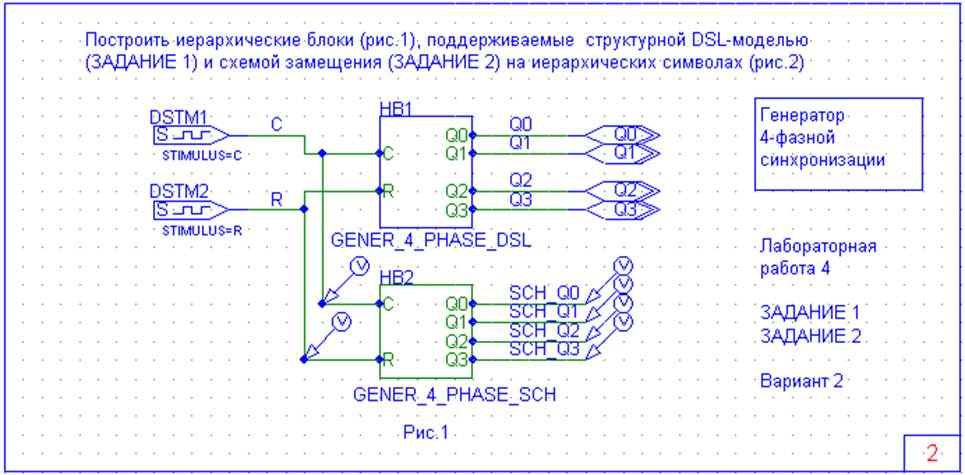

ЗАДАНИЕ 1. Проектирование структурных DSL-моделей. Ориентировочное время выполнения задания – 60 мин. (1,5 балла).

|

Рис.1. Пример задания на проектирование

структурной DSL-модели

генератора 4-фазной синхронизации

Лабораторная работа 4 во многом напоминает предыдущую работу. Там вы создавали иерархические блоки, поддерживаемые DSL-моделью и схемой замещения. Нечто похожее предстоит делать и здесь. Разница в том, что вместо поведенческой модели теперь необходимо построить структурную DSL-модель, а схема замещения должна быть выполнена на «самодельных» иерархических символах (рис.2).

Другими словами, в ЗАДАНИИ 1 вам надо описать элементы схемы и структурные связи не графическими инструментами (УГО и проводниками), а DSL-кодом. Возможное решение показано на рис.3.

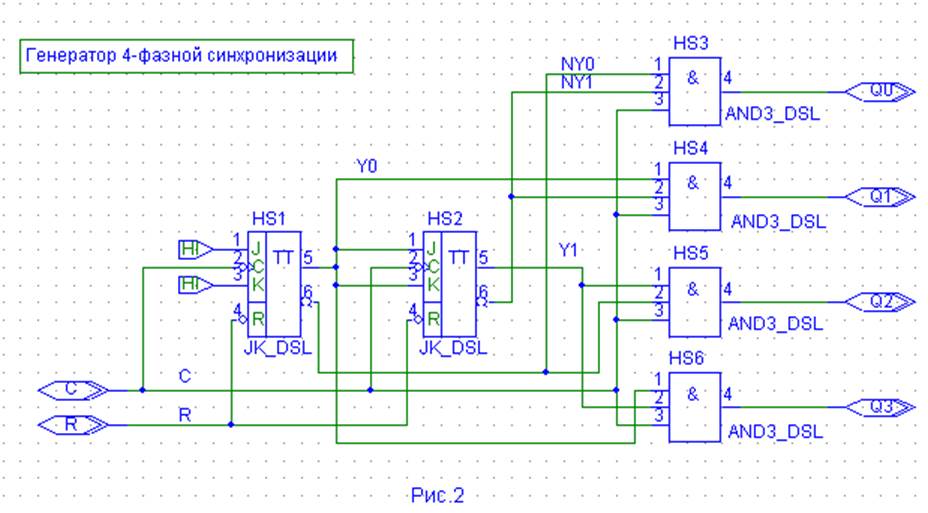

|

Рис.2. Графическое описание структуры

генератора 4-фазной синхронизации

в виде схемы замещения

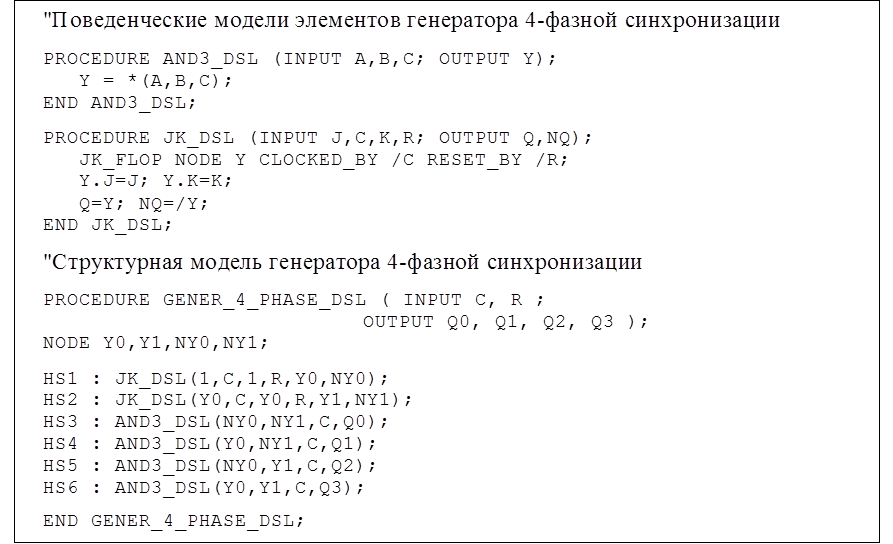

Рис.3. Текстовое описание структуры генератора 4-фазной

синхронизации

на языке DSL

Приступая к работе, постройте сначала поведенческие DSL-модели различных элементов схемы. Каждую модель надо оформить в виде отдельной процедуры. Затем напишите DSL-код всего узла, используя информацию о его структуре. Из рисунка 3 видно, что модель всего объекта представляется композицией (объединением) моделей отдельных элементов. Структурные связи без труда просматриваются в списках фактических параметров процедур.

Модели элементов удобно строить с помощью DSL-шаблонов, своеобразных «заготовок». Они вызываются командой Insert/DSL Template из встроенного текстового редактора Text Editor. Особенно полезны такие шаблоны для построения моделей различных типов триггеров.

Выполните моделирование своего проекта и добейтесь, чтобы всё работало правильно. После этого перенесите DSL-модели элементов в отдельный файл, откомпилируйте его программой PLSyn (команда Tools/Compile library…) и сделайте на него ссылку из своего проекта (например, USE ‘lib_dsl_proc’). Убедитесь, что моделятор находит необходимые модели (файл с расширением afb).

ЗАДАНИЕ 2. Проектирование иерархических блоков, поддерживаемых схемами замещения на иерархических символах. Ориентировочное время выполнения задания – 60 мин. (1,5 балла).

Перед тем, как рисовать схему замещения, необходимо построить иерархические символы, из которых она состоит (рис.2). С технологией создания таких символов вы должны были познакомиться на предыдущей лабораторной работе. Она довольно проста. Сначала создается иерархический блок, для него пишется DSL-модель, после чего блок конвертируется в символ по команде Edit/Convert Block…. Все созданные символы следует поместить в одну библиотеку. После этого рисуется схема замещения так, как это показано на рис.2.

Созданную схему необходимо промоделировать и убедиться, что она правильно функционирует.

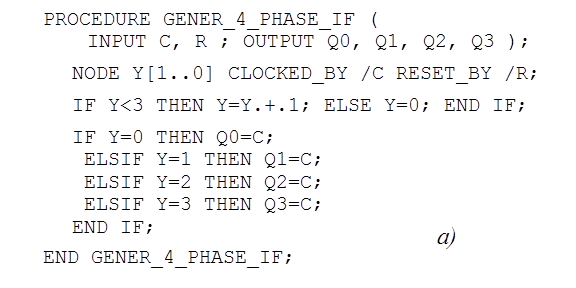

ЗАДАНИЕ 3. Проектирование поведенческих DSL-моделей. Ориентировочное время выполнения задания – 30…60 мин. (1…2 балла).

Цель третьего задания – познакомиться с различными способами построения поведенческих DSL-моделей. Некоторый опыт этой работы вы должны были получить, выполняя ЛР3 (ЗАДАНИЕ 1).

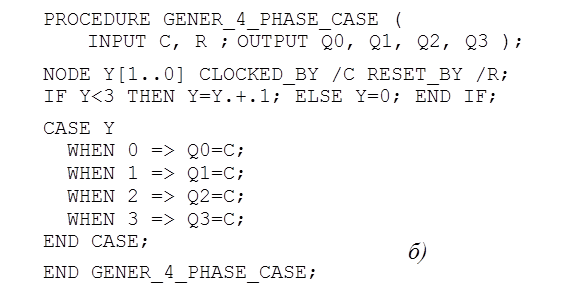

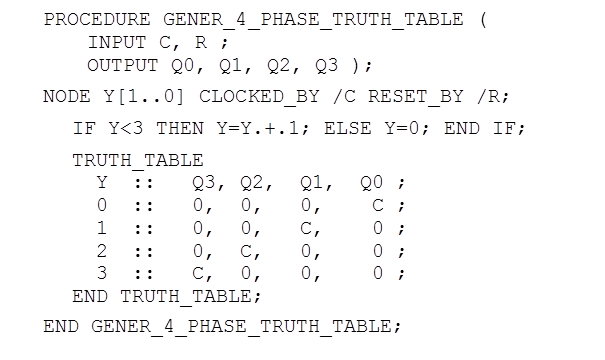

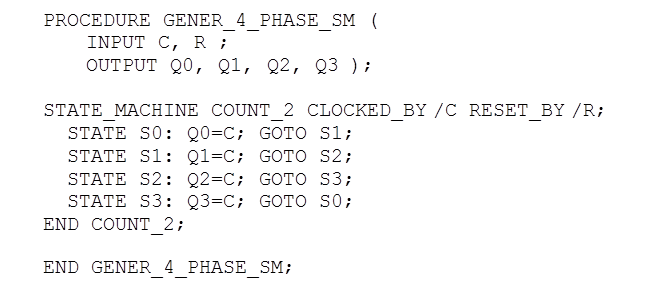

В языке DSL используются четыре оператора – IF, CASE, TRUTH_TABLE и STATE_MACHINE. Вам предоставляется возможность продемонстрировать умение работать с каждым из них. Любой работающей вариант DSL-модели «стоит» 0,5 балла. На рис.4 показаны возможные решения для генератора 4-фазной синхронизации.

Рис.4. Варианты построения поведенческих

DSL-моделей с использованием

различных операторов (IF,

CASE, TRUTH_TABLE, STATE_MACHINE)

Желательно все варианты DSL-моделей проектировать и сохранять в одном файле. Проще всего это сделать так. Испытав первую модель, вы выделяете иерархический блок с этой моделью, и редактируете его атрибут PLMODEL. Например, заменяете значение GENER_4_PHASE_IF на GENER_4_PHASE_CASE. Редактор, не найдя по ссылке такой процедуры, создаст новый шаблон DSL-модели, куда вы и поместите свой код.

ЗАДАНИЕ 4. Проектирование потоковых DSL-моделей. Ориентировочное время выполнения задания – 30 мин. (1 балл).

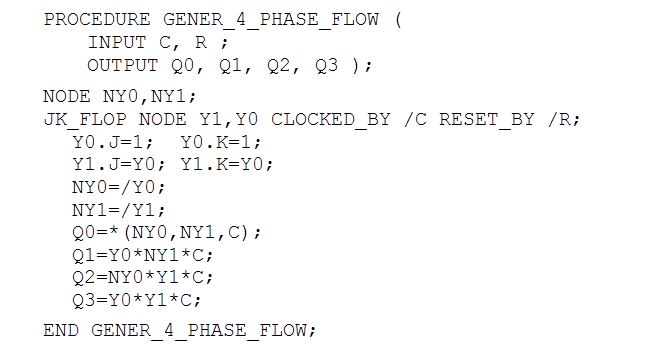

Потоковые модели занимают промежуточное положение (нишу) между поведенческими и структурными моделями. Они используют информацию о структуре объекта, однако элементы структуры не оформляются в виде обособленных моделей, как это делается для структурной модели объекта.

Пример потоковой модели генератора 4-фазной синхронизации показан на рис.5. Сравнивая этот текст с графическим описанием структуры генератора (рис.2), легко заметить, что в потоковой модели неявно присутствуют все его элементы. Триггеры Y1 и Y0 объявлены в строке:

JK_FLOP NODE Y1,Y0 CLOCKED_BY /C RESET_BY /R;

Их инверсные выходы заданы описанием: node NY0, NY1;. Элементы 3И описаны строчками: Q0=*(NY0, NY1, C); …Q3=Y0*Y1*C;

Структурные связи тоже неявно присутствуют в описании. Например, выход триггера Y0 подключён к J и K входам триггера Y1. Эта связь описана строкой: Y1.J=Y0; Y1.K=Y0;

Рис.5. Потоковая DSL-модель генератора 4-фазной синхронизации

Попробуйте построить потоковую модель для своего варианта задания, выполните её функциональную верификацию и добейтесь, чтобы она показывала такие же результаты, как и ранее выполненные DSL-модели.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.