Программа выполнения лабораторной работы 4

в САПР OrCAD 9.1

Цель работы - научиться проектировать VHDL – модели цифровых элементов и узлов:

· на основе функционального (поведенческого) описания объекта;

· на основе потокового представления объекта;

· на основе структурного описания объекта.

Перед началом работы создайте свою папку, например LAB4_OrCAD, в которой будут сохраняться все результаты выполненных заданий.

ЗАДАНИЕ 1.

Проектирование и моделирование цифровых схем на абстрактных логических элементах. Ориентировочное время выполнения задания – 90 мин. (2 балла).

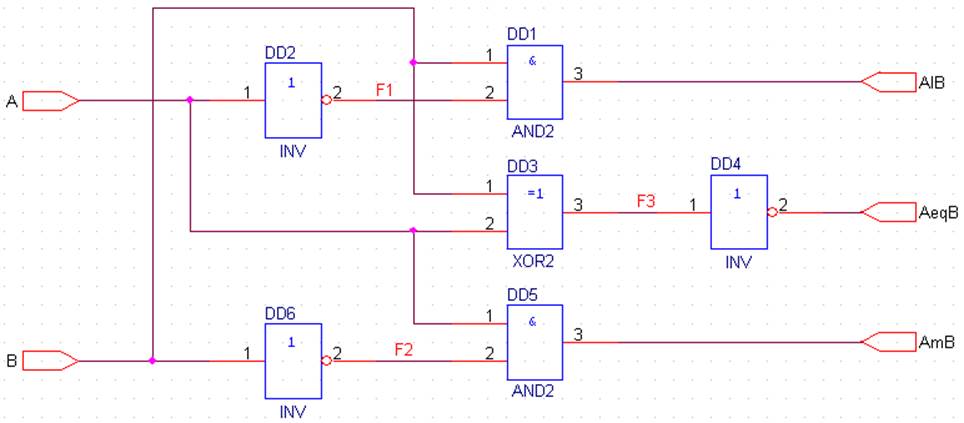

Получите у преподавателя конкретный вариант задания. Пример такого задания показан на рис.1.

Рис.1. Пример задания на проектирование и моделирование

простой схемы

на абстрактных компонентах (comparator)

1.1. Запустите графический редактор OrCAD Capture и откройте свою библиотеку символов my_lib.olb. Спроектируйте в ней графические описания логических элементов, которые используются в вашем задании. В данном примере – это INV, AND2 и XOR2.

1.2. Создайте новый проект, например lab4_z1.opj и нарисуйте в нём требуемую схему (рис.1). Сделайте в том же проекте ещё одну схемную папку, и методом D&D скопируйте в неё только что нарисованную схему. Замените абстрактные компоненты аналогичными по выполняемым функциям системными компонентами. В данном примере – это 74ls04 (INV), 74ls08 (AND2) и 74ls86 (XOR2).

Теперь у вас есть две схемы, выполняющие одну и ту же функцию одноразрядного компаратора. Переименуйте папки так, чтобы первая называлась comp_RUS, а вторая – comp_LS.

1.3. Создайте новую схемную папку и сделайте её папкой верхнего уровня (команда MakeRoot). Разместите на схеме верхнего уровня два иерархических блока: comp_RUS и comp_LS. Интерфейсные контакты должны появиться автоматически, так как используется технология проектирования иерархических блоков «снизу-вверх».

1.4. Подготовьте схему для тестирования, задав на оба блока одинаковые наборы входных сигналов, и промоделируйте её. Измерьте задержки и добейтесь, чтобы они были одинаковыми для обоих блоков. Понятно, что корректировать надо задержки у абстрактных элементов.

ЗАДАНИЕ 2.

Проектирование поведенческих VHDL – моделей цифровых узлов. Ориентировочное время выполнения задания – 60 мин. (1,5 балла).

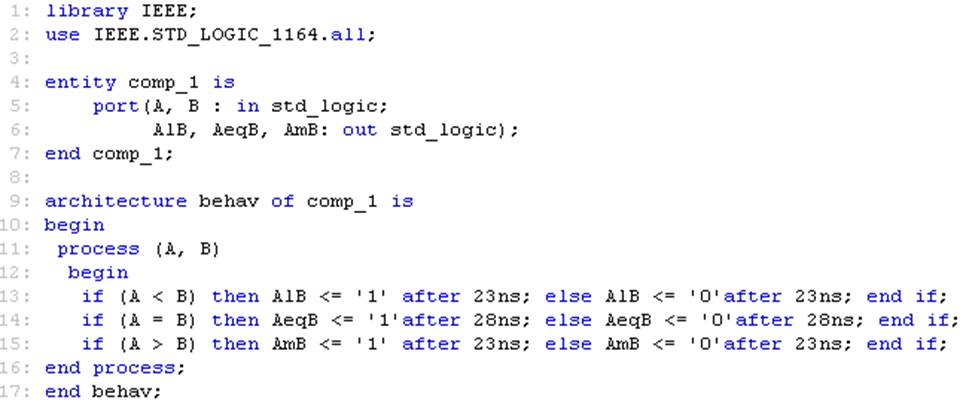

2.1. Создайте новый проект, например lab4_z2.opj и исполните команду File/NewVHDLFile. Используя шаблоны Simples…, напишите текст поведенческой VHDL – модели (рис.2).

Рис.2. Пример реализации поведенческой VHDL– модели

одноразрядного компаратора comp_1

2.2. Обратите особое внимание на величины задержек, они должны быть такими же, что и для схемы, спроектированной по заданию 1. Устраните возможные ошибки и сохраните модель в файле comp_1.vhd.

2.3. Разместите на схеме верхнего уровня иерархический блок, «начинкой» которого является только что созданная VHDL – модель. Протестируйте свой проект и убедитесь, что поведение узла соответствует логике его работы, а величины задержек совпадают с экспериментами, выполненными в задании 1.

ЗАДАНИЕ 3.

Проектирование потоковых VHDL – моделей цифровых узлов. Ориентировочное время выполнения задания – 30 мин. (1 балл).

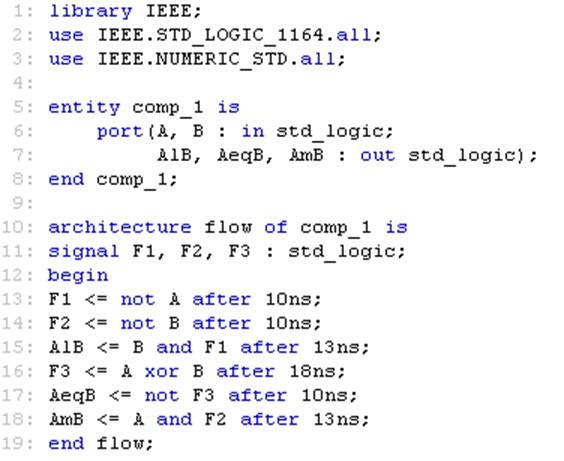

3.1. Создайте новый проект, например lab4_z3.opj и исполните команду File/NewVHDLFile. Используя шаблоны Simples…, напишите текст потоковой VHDL – модели (рис.3).

Рис.3. Пример реализации потоковой VHDL– модели

одноразрядного компаратора comp_1

3.2. Обратите особое внимание на величины задержек, они должны быть такими же, что и для схемы, спроектированной по заданию 1. Устраните возможные ошибки и сохраните модель в файле comp_1.vhd.

3.3. Разместите на схеме верхнего уровня иерархический блок, «начинкой» которого является только что созданная потоковая VHDL – модель. Протестируйте свой проект и убедитесь, что функционирование узла соответствует логике его работы, а величины задержек совпадают с экспериментами, выполненными в задании 1.

ЗАДАНИЕ 4.

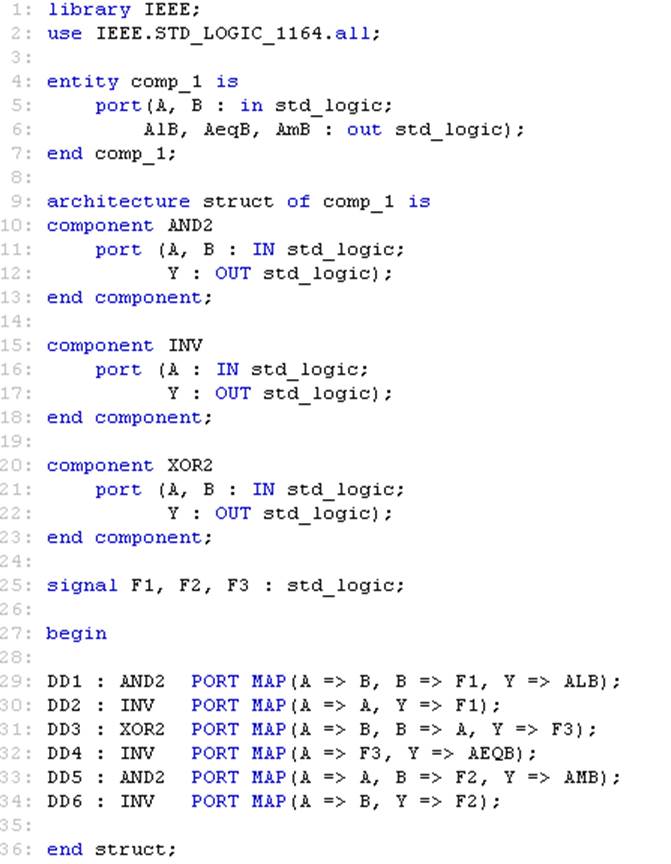

Проектирование структурных VHDL – моделей цифровых узлов. Ориентировочное время выполнения задания – 30 мин. (1 балл).

3.1. Создайте новый проект, например lab4_z4.opj и исполните команду File/NewVHDLFile. Используя шаблоны Simples…, напишите текст структурной VHDL – модели (рис.4).

Рис.4. Пример реализации структурной VHDL– модели

одноразрядного компаратора comp_1

4.2. Обратите особое внимание на величины задержек, они должны быть такими же, что и для схемы, спроектированной по заданию 1. Устраните возможные ошибки и сохраните модель в файле comp_1.vhd.

4.3. Разместите на схеме верхнего уровня иерархический блок, «начинкой» которого является только что созданная структурная VHDL – модель. Протестируйте свой проект и убедитесь, что функционирование узла соответствует логике его работы, а величины задержек совпадают с экспериментами, выполненными в задании 1.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.