elsif rising_edge(C) then

if (TEMP_Q = "100") then

TEMP_Q <= (others => '0');

else

TEMP_Q <= TEMP_Q + 1;

end if;

end if;

end process;

Q0 <= TEMP_Q(0);

Q1 <= TEMP_Q(1);

Q2 <= TEMP_Q(2);

end architecture;

Рис.4.

Один из возможных вариантов VHDL -

модели двоичного суммирующего

счётчика по модулю 5

2.3. Попробуйте разобраться с описанием VHDL – модели. Откомпилируйте

созданный файл (пиктограмма ![]() )

и устраните возможные ошибки.

)

и устраните возможные ошибки.

2.4. Активизируйте редактор временных диаграмм Waveform (кнопка ![]() ), сформируйте список сигналов

для наблюдения и задайте для входных сигналов C

и R

эпюры напряжений.

), сформируйте список сигналов

для наблюдения и задайте для входных сигналов C

и R

эпюры напряжений.

2.5. Промоделируйте свой проект на заданном наборе внешних воздействий и добейтесь его правильного поведения. Результаты моделирования сохраните в файле, например count5_HDE.awf.

2.6. Добавьте в исходный VHDL – код две задержки: «по сбросу» - 10ns и «по счёту» - 15ns. Перекомпилируйте файл и повторите моделирование счётчика. Убедитесь, что на результирующих временных диаграммах наблюдаются именно эти величины задержек.

ЗАДАНИЕ 3. Проектирование иерархических блоков.

Ориентировочное время выполнения задания – 60 мин. (2,0 балла).

3.1. Запустите программу схемного редактора и

разместите в его рабочей области иерархический блок (команда Fub из меню Diagram или пиктограмма

![]() ). Стандартное имя блока Fub1 замените на decoder4_hde. Желательно, чтобы имя

блока несло информацию о том, каким способом будет создано его внутреннее описание.

В первом случае – это VHDL –

код. Потом вам надо будет создать ещё три блока: со схемой замещения, диаграммой

состояний и с EDIF – списком

цепей.

). Стандартное имя блока Fub1 замените на decoder4_hde. Желательно, чтобы имя

блока несло информацию о том, каким способом будет создано его внутреннее описание.

В первом случае – это VHDL –

код. Потом вам надо будет создать ещё три блока: со схемой замещения, диаграммой

состояний и с EDIF – списком

цепей.

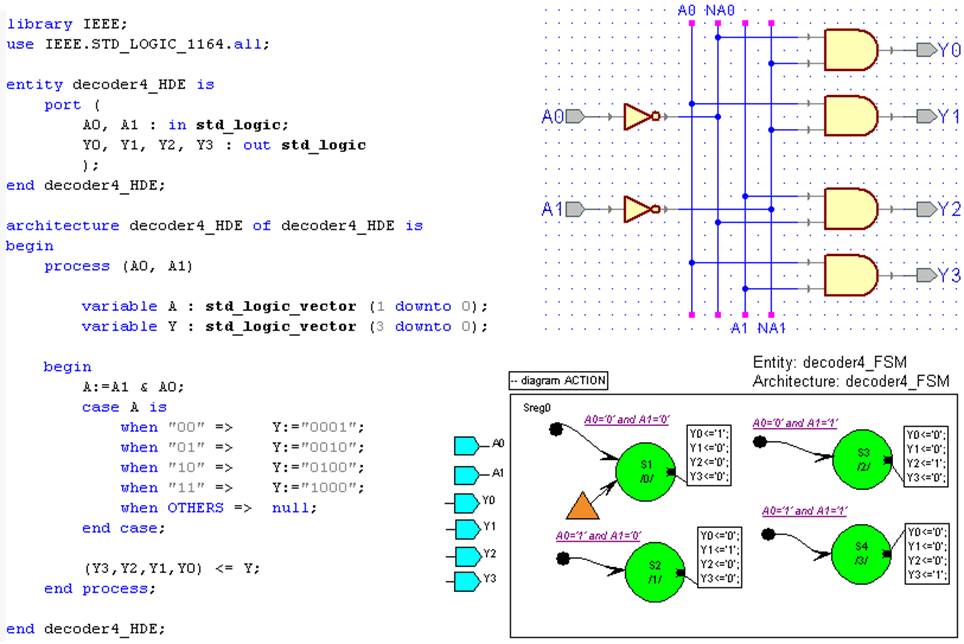

По названию блока понятно, что он будет имитировать работу дешифратора на два входа A0, A1 и четыре выхода Y0, Y1, Y2, Y3. Подведите к блоку входные и проводники, понизьте его уровень и напишите (или сгенерируйте) его VHDL – модель.

Таким же способом постройте ещё три блока decoder4_bde, decoder4_fsmи decoder4_edif соответственно со схемой, диаграммой и EDIF – списком цепей.

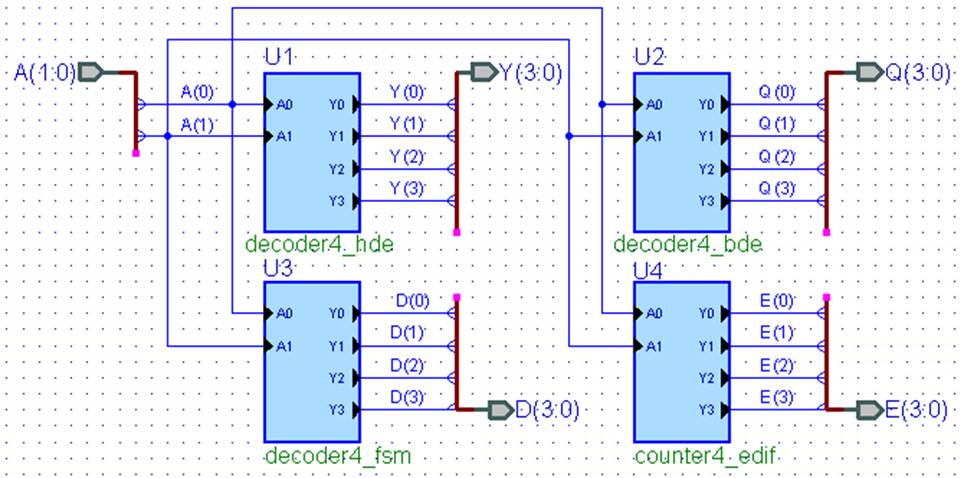

Каждая реализация иерархического блока оценивается в 0,5 балла. В конечном итоге проект должен приобрести вид, изображённый на рис.5.

Рис5. Иерархическая схема с тремя блоками,

реализующими разными способами

функцию дешифратора на два входа и четыре выхода

Внутреннее содержание блоков показано на рис.6. Закончив проектирование и моделирование иерархических блоков, сохраните текущую версию проекта (команда Backuprevision из меню Design). Дело в том, что, конвертировав иерархический блок в символ, вы уже не сможете вернуться назад.

Рис.6. Способы представления содержимого иерархических

блоков дешифратора

(EDIF – список цепей не приводится из-за большого объёма)

3.2. Преобразуйте блоки в символы. Эта операция выполняется одной командой ConvertFubtoSymbol, вызываемой из контекстного меню. Обратите внимание, в окне менеджера библиотек LibraryManager вместо трёх строчек с названием Fub появится другой текст: Symbol = Yes.

3.3. Повторите моделирование схемы, в которой блоки конвертированы в символы, чтобы убедиться, что проект сохранил свою работоспособность.

ЗАДАНИЕ 4. Освоение технологии функционального моделирования в среде DesignFlowManagerпакета Active-HDL 7.1.

Ориентировочное время выполнения задания – 15 мин. (0,5 балла).

4.1. Создайте в своём рабочем пространстве новый проект Lab3 и добавьте в него из проекта Lab1 (первая лабораторная работа) исходные файлы с моделями разработанных вами элементов и триггеров (в нашем примере and2_my.vhd, xor_my.vhd, inv_my.vhd, dff_my.vhd). При выполнении этой операции установите флажок Makelocalcopy, чтобы сделать в новом проекте локальные копии, а не ссылки.

Добавьте сюда же схемное описание разработанного цифрового узла на ваших элементах, то есть файл count5_BDE_my.vhd.

4.2. Из проекта Lab2 добавьте ещё два файла: диаграмму состояний (файл count5_FSM.adf) и описание узла на языке VHDL (файл count5_HDE.vhd). Теперь у вас есть три варианта описания проекта: код на языке VHDL, схема и диаграмма состояний. Откомпилируйте все полученные файлы.

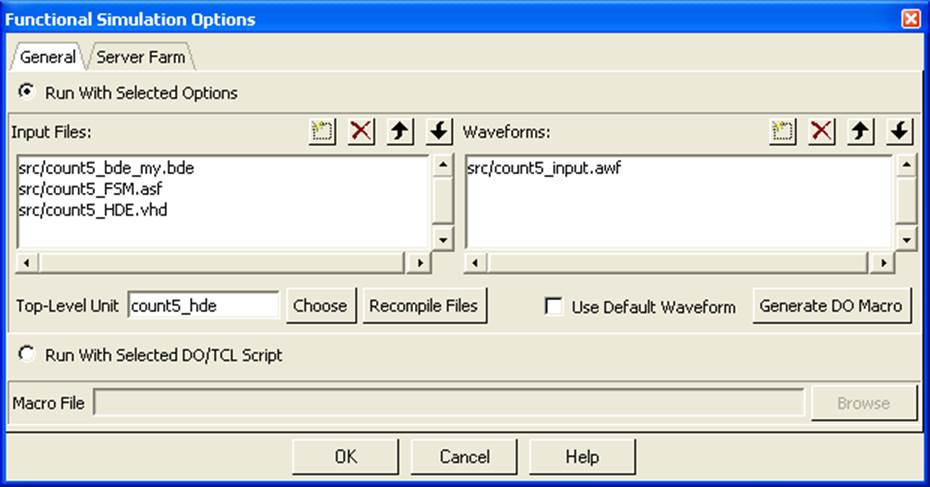

4.3. Активизируйте закладку designflow и нажмите кнопку options (рис.7) рядом с пиктограммой functionalsimulation.

Рис.7. Устанавливаем опции для функционального моделирования

На открывшейся диалоговой панели FunctionalSimulationOptions сделайте установки, как показано на рис.8. Если у вас не было файла с временными диаграммами входных сигналов count5_input.awf, то создайте его. В поле Top-LevelUnit поочерёдно задавайте имя модуля верхнего уровня, чтобы промоделировать все три варианта вашего проекта на одном и том же наборе входных сигналов.

Рис.8. Диалоговая панель установок для выполнения функционального моделирования

Учтите, что нажатие на кнопку functionalsimulation (см. рис.7) не выполняет моделирование, а только инициализирует его. Убедитесь, что все варианты описания проекта соответствует заданию, и показывают правильные реакции на внешние воздействия.

Сводную временную диаграмму сохраните в файле count5_all.awf, чтобы показать её преподавателю.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.