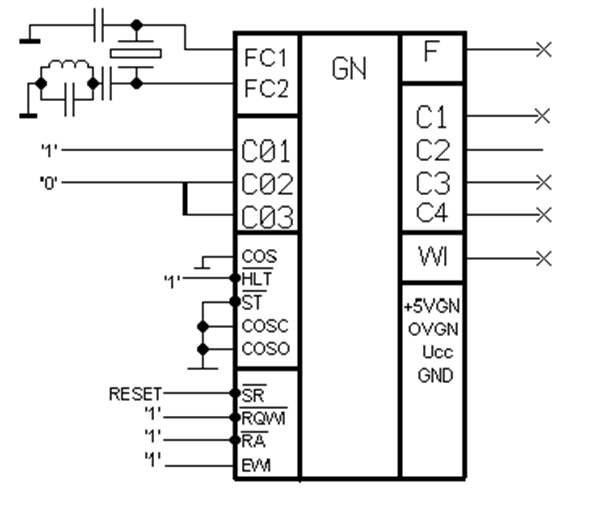

Генератор позволяет формировать 8 различных опорных синхропоследовательностей (F3 – F10) на выходах С1 – С4. Для формирования синхросигнала в данном проекте был избран выход С1 и синхропоследовательность F4 (СО3=”0”, CO2=”0”, CO1=”1”), т.е. тактовый сигнал разделен на четыре микротакта и имеет нулевое значение на последнем микротакте и единичное на первых трех. Сигнал с выхода С1 объединен схемой И с сигналом RST# c блока

Начальной установки для того, чтобы не выдавать синхросигнал раньше времени предустановки. Генератор всегда работает в режиме «Работа», входы задающие режим «Ожидание» заземлены. На вход SR# подается сигнал с блока начаольной установки, запускающий генератор в начальный момент после включения питания.

Схемная обвязка генератора взята из литературы [4], управляющие входы подключены в соответсвии с небходимым режимом работы.

Cхема включения КМ1804ГГ1

|

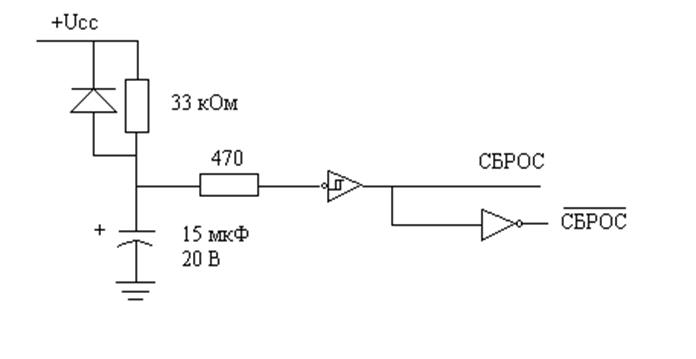

13. Схема начальной установки.

Данная схема начальной установки рекомендована в работе [8].

Последовательно включенный со входом вентиля резистор необходим для того, чтобы избежать повреждение схемы при отключении схемы,так как в противном случае электролитический конденсатор будет пытаться запитаь систему через защитный диод входного вентиля. Символ гистерезиса на рисунке означает, что на входе инвентора установлен триггер Шмитта, собранный, например, на 74LS14(6 инверторов).

Схема начальной установки

14. Разработка функциональной и принципиальной схем памяти.

В структуре использубтся два типа памяти: ОЗУ и ПЗУ. ОЗУ представляет собой динамическую память с произвольной выборкой. В качестве ПЗУ используется EPROM память. Подбор микросхем осуществлялся по следующим критериям:

- Необходимая информационная организация;

- Динамические харатеристики;

- Совместимость электрического интерфейса;

- Экономичность;

По всем этим критериям были подобраны следующие приборы:

- DRAM – SIMM компании Samsung КММ5361203С2W/C2WG с максимальным временем доступа 50 нс и со внутренней организацией 1Мх36бит. Данная микросхема удовлетворяет нашему проекту по своим временным характеристикам и организации – 32 информационных разряда и 4 паритетных разряда, имеет ТТЛ совместимые входы и выходы, выполняет циклы регенерации ROR, CBR, Hidden Refresh;

- PROM – Am29F100 фирмы AMD с максимальным временем доступа 70 нс и внутренней организацией 64Кх16 бит.

Управляющие сигналы, необходимые для функционорования блоков памяти берутся из соответствующих разрядов микрокоманды. Для бесконфликтого использования шины данных для ОЗУ и ПЗУ предусмотрен выбор типа памяти старшим, 21- разрядом адреса. Тем самым адресное пространство ОЗУ и ПЗУ оказывается совмещенным, что позволяет использовать ЗУ большой емкости, но исключает возможность совместного их использования. В данном проекте это не важно, так как шина входных и выхожных данных совмещена и одновременное использование памати все равно не возможно.

ОЗУ: Конторль паритета для данных в динамической памяти организован следующим образом:

Так как в операционном блоке и устройстве управления контрль паритета для данных не приеняется, то шина данных в данном проекте согласно разрядности ЦП 32-разрядная. Следовательно, нужно организовывать вычисление паритетных битов непостредственно перед записью данных в память и занесение их туда, а затем при считывании снова сворачивать 32 информационных разряда и сравнивать их с теми контрольными разрядами, которые хранились в памяти. Данные свертки и сравнения делаются с помощью 5 генераторов паритетных битов (в каждом генераторе генерируется один паритетный бит на байт данных) фирмы Texas Instruments – SN54180. Четыра из них отвечают за свертку информацоинных разрядов, а один непосредственно за сравнение паритетных битов, хранящихся в памяти и информационных разрядов считываемых из нее. Схема организации контроля паритета приведена на принципиальной схеме.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.