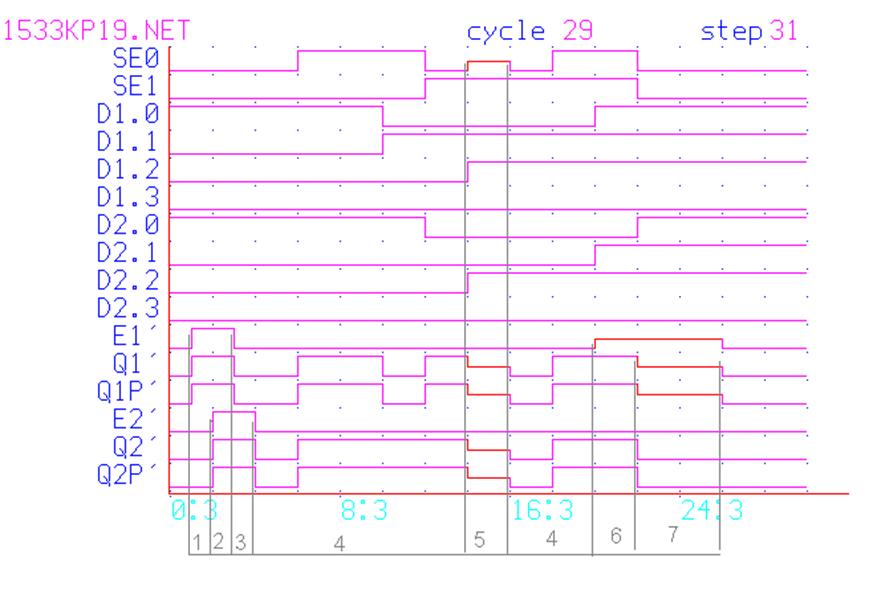

Рис.

5 Временная диаграмма всех

Рис.

5 Временная диаграмма всех

возможных режимов работы узла.

1 - Режим запрещения работы 1-ого мультиплексора в корпусе. (на выходе Н уровень).

2 - Режим запрещения работы 1- ого и 2- ого мультиплексоров (на выходах Н уровень)

3 - Режим запрещения работы 2-ого мультиплексора в корпусе. (на выходе Н уровень).

4 - Режим работы 1- ого и 2- ого мультиплексоров (на выходах Q1# (Q1P#) и Q2# (Q2P#) информация от выбранных входами SE0, SE1 информационных входов D1.0 – D1.3, D2.0 – D2.3)

5 - Режим при котором выходы 1- ого и 2- ого мультиплексоров находятся в «Х» состоянии. Это происходит в следствии того, что адрес SE0 находится в «Х» состоянии и на входы данных D1.2 и D2.2 подается сигнал высокого уровня. (на 3-х входах элементов DD6 и DD17 (см. рис.2) сигналы высокого уровня, а на одном – «Х», следовательно на их выходах «Х» состояние).

6 - Режим, при котором несмотря на «Х» состояние на входе Е1# на выходе 1-ого мультиплексора наблюдается Н состояние, т.к. на входе D1.3 сигнал низкого уровня.

7 - Режим, при котором выход 1-ого мультиплексора в «Х» состоянии, т.к. E1# = «X» и D1.0 = «Н»

По данной диаграмме можно сделать вывод о том, что обе реализации (Q1#,Q2# - выходы иерархического символа, а Q1P#, Q2P# - выходы узла, поддерживаемого PML моделью (см. рис. 4)) полностью идентичны и их результаты полностью совпадают.

Командный файл для моделирования схемы программой

PC-LOGSс учетом реальных задержек.

LOAD kp19pt1.NET

LOAD 1533kp19.NET

CYCLE 32

DISPLAY 4/1

PROBE SE0 SE1 D1.0 D1.1 D1.2 D1.3 D2.0 D2.1 D2.2 D2.3 E1' Q1' Q1p'

gen [0 0] E1' (0/1 1/2 0/26)

gen [0 0] E2' (0/26 1/10)

gen [0 0] SE0 (0/6 1/6 0/6 1/4 0/10)

gen [0 0] SE1 (0/12 1/10 0/10)

gen [0 0] D1.0 (1/10 0/10 1/10)

gen [0 0] D1.1 (0/20 1/35)

gen [0 0] D1.2 (0/14 1/2 0/20)

gen [0 0] D1.3 (0/35)

gen [0 0] D2.0 (1/10 0/10 1/10)

gen [0 0] D2.1 (0/20 1/35)

gen [0 0] D2.2 (0/14 1/2 0/20)

gen [0 0] D2.3 (0/35)

CLOCK RUL 1(0/32 1/18 0/46 1/20 0/76 1/24 0/232 1/18 0/46 1/13 0/179 1/21 0/107 1/18 0/10)

probe RUL E2' Q2' Q2p'

spool all

SIM 30

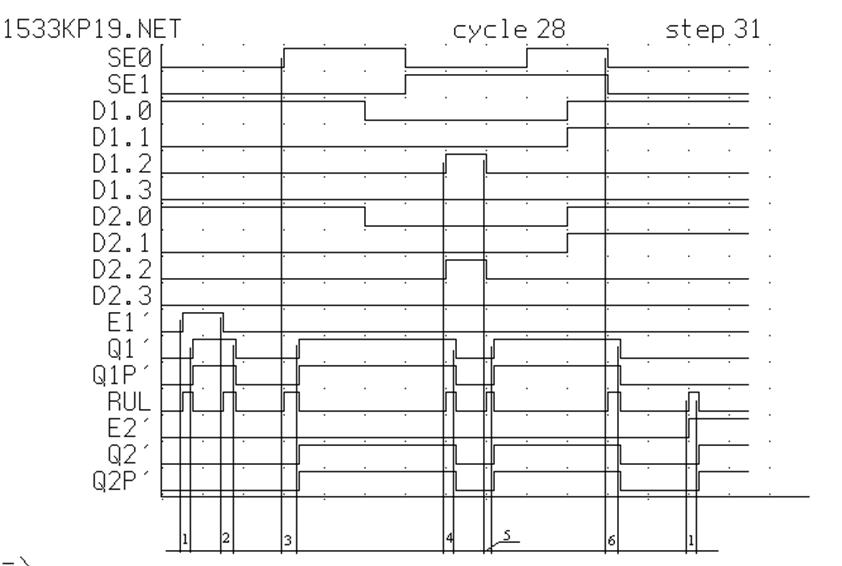

Результаты логико – временного моделирования заданной

схемы в пакете PCAD с учетом реальных задержек.

1 - Задержка распространения сигнала по фронту от входа E*# до выхода Q*# (18нс.)

2 - Задержка распространения сигнала по срезу от входа E*# до выхода Q*# (20нс.)

3 - Задержка распространения сигнала по фронту от входа SE0 до выходов Q*# (24нс.)

4 - Задержка распространения сигнала по фронту от входов D* до выходов Q*# (18нс.)

5 - Задержка распространения сигнала по срезу от входов D* до выходов Q*# (13нс.)

6 - Задержка распространения сигнала по срезу от входов SE0, SE1 до выходов Q*# (21нс.)

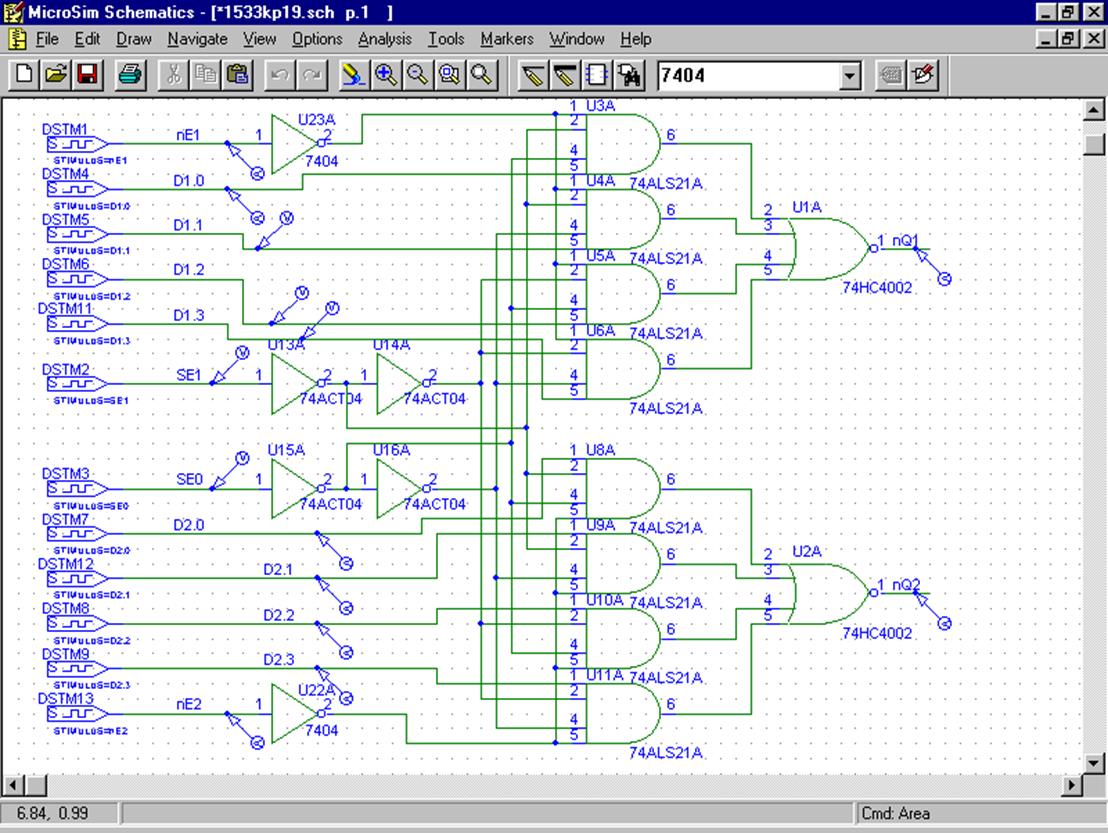

Моделирование в пакете PSPICE (DesignLab_8)

Принципиальная схема.

Рис. 7 Принципиальная схема моделируемого узла (КР1533КП19)

Текстовое SPICE - описание моделируемого узла.

файл 1533kp19.cir

* C:\Program Files\DesignLab8\Projects\1533kp19.sch

* Schematics Version 8.0 - July 1997

* Tue Jun 06 15:18:56 2000

** Analysis setup **

.tran 1ns 1000ns

.INC "kp19a.stl"

* From [SCHEMATICS NETLIST] section of msim.ini:

.lib "nom.lib"

.INC "1533kp19.net"

.INC "1533kp19.als"

.probe

.END

файл 1533kp19.net

* Schematics Netlist *

X_U15A SE0 $N_0001 $G_DPWR $G_DGND 74ACT04 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_U13A SE1 $N_0002 $G_DPWR $G_DGND 74ACT04 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_U16A $N_0001 $N_0003 $G_DPWR $G_DGND 74ACT04 PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

X_U4A $N_0005 $N_0002 $N_0003 D1_1 $N_0004 $G_DPWR $G_DGND 74ALS21A

+ PARAMS:

+ IO_LEVEL=0 MNTYMXDLY=0

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.