|

Обозначение |

Время распространения сигнала: |

Максимальное значение, нс |

|

tPLH |

- от выводов SE1,SE0 к выводам Q1# ,Q2# - от выводов D1.3-D1.0 (D2.0-D2.3) к выводу Q1# (Q2#) - от выводов E1#, E2# к выводам Q1# ,Q2# |

24 18 18 |

|

tPHL |

- от выводов SE1,SE0 к выводам Q1# ,Q2# - от выводов D1.3-D1.0 (D2.0-D2.3) к выводу Q1# (Q2#) - от выводов E1#, E2# к выводам Q1# ,Q2# |

21 13 20 |

Описание работы узла.

Сдвоенный селектор – мультиплексор 4 в 1.

Мультиплексор работает при наличии на входах Е1#, Е2# низкого уровня напряжения. При этом на выходы Q1#, Q2# подается информация от выбранных входами SE0, SE1 информационных входов D1.0 – D1.3, D2.0 – D2.3(см. табл. 2, режим Работа).

При наличии на входах Е1#, Е2# высокого уровня напряжения, выходы Q1#, Q2# устанавливаются в состояние высокого уровня напряжения (см. табл. 2, режим Запрещение работы)

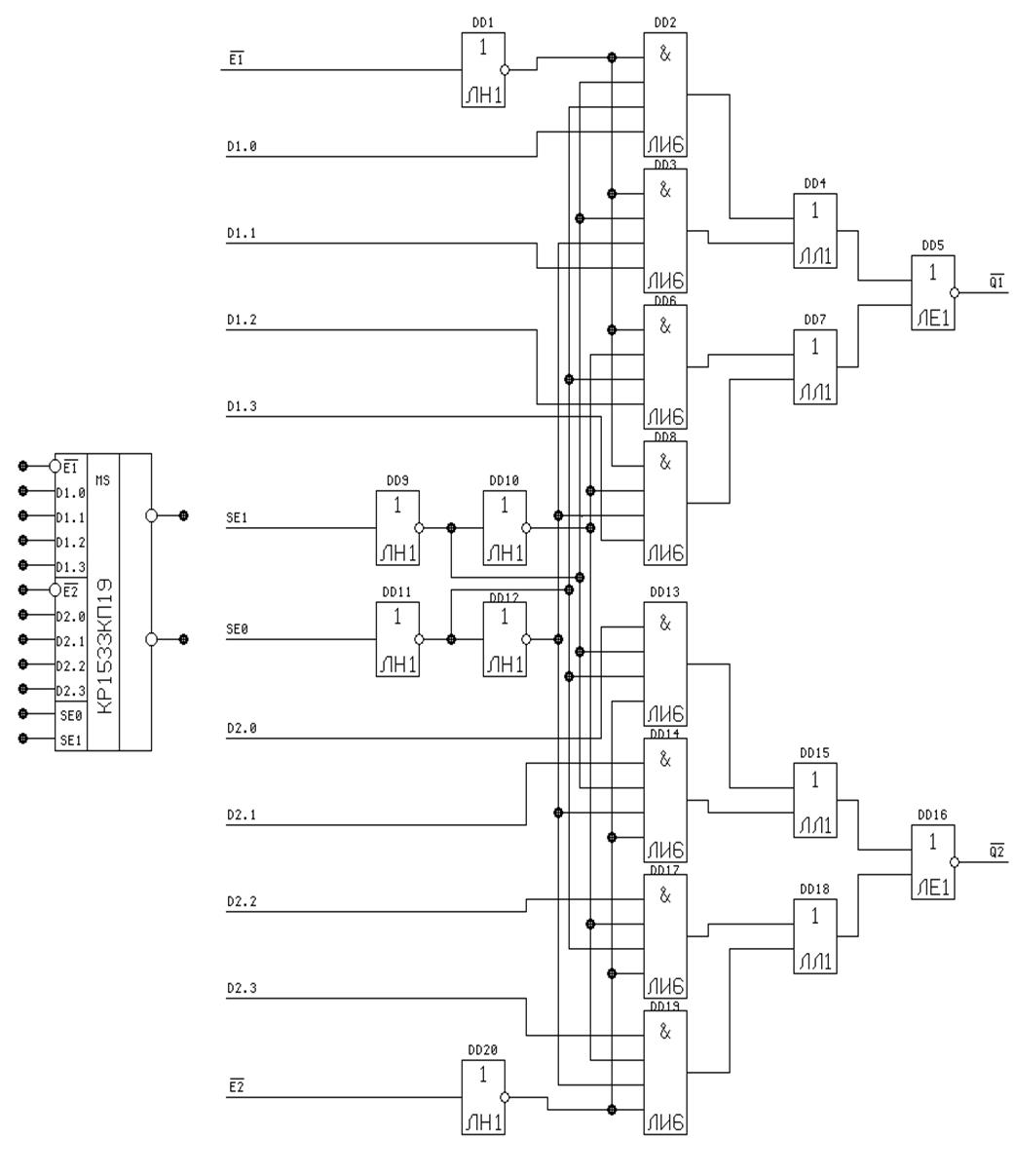

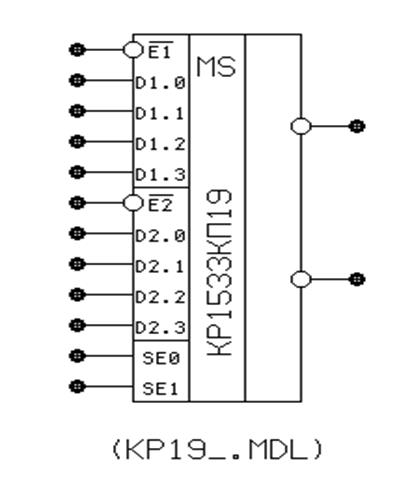

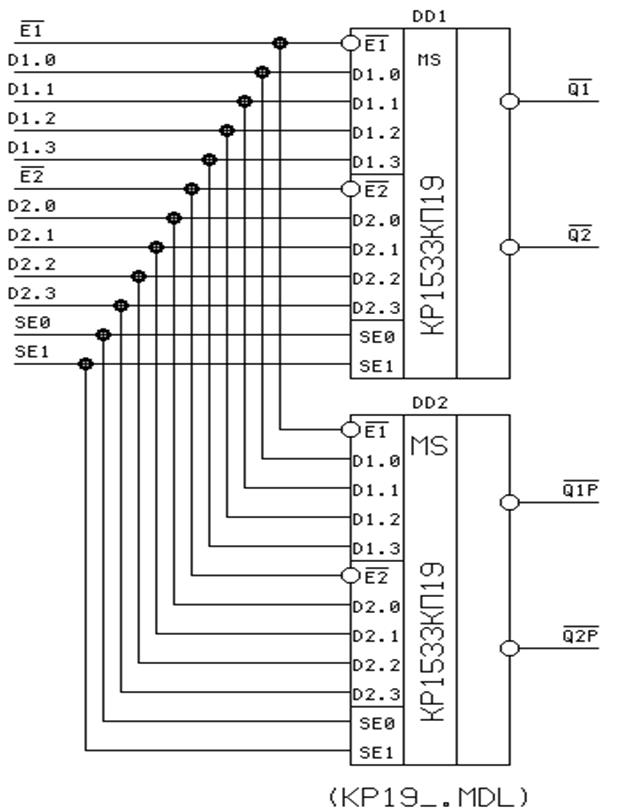

Макромодель, представленная как иерархический символ.

Рис. 2 Внешнее описание узла в виде

графического изображения и внутреннее описание в виде логической структуры на

вентильном уровне.

|

Поведенческая модель на языке PML.

pml_kp19 ()

INPUT E1', E2', SE0, SE1, D1.0, D1.1, D1.2, D1.3, D2.0, D2.1, D2.2, D2.3;

OUTPUT Q1', Q2';

LOCAL E,QQ1,QQ2;

{ IF(E!="0") {QQ1=(~E1'&((D1.0&~SE0&~SE1)|(D1.1&SE0&~SE1)|(D1.2&~SE0&SE1)|(D1.3&

SE0&SE1))) (0,0,"d","d");

QQ2=(~E2'&((D2.0&~SE0&~SE1)|(D2.1&SE0&~SE1)|(D2.2&~SE0&SE1)|(D2.3&

SE0&SE1))) (0,0,"d","d");E="0";

} // Для начальной инициализации схемы.

IF(SE0=="/")|(SE0=="\")|(SE1=="/")|(SE1=="\")

{QQ1=(~E1'&((D1.0&~SE0&~SE1)|(D1.1&SE0&~SE1)|(D1.2&~SE0&SE1)|(D1.3&SE0&SE1))) (21,24,"d","d");

QQ2=(~E2'&((D2.0&~SE0&~SE1)|(D2.1&SE0&~SE1)|(D2.2&~SE0&SE1)|(D2.3&

SE0&SE1))) (21,24,"d","d");

}

IF((D1.0=="/")|(D1.0=="\")|(D1.1=="/")|(D1.1=="\")|(D1.2=="/")|(D1.2=="

\")|(D1.3=="/")|(D1.3=="\"))

QQ1=(~E1'&((D1.0&~SE0&~SE1)|(D1.1&SE0&~SE1)|(D1.2&~SE0&SE1)|(D1.3&

SE0&SE1))) (18,13,"d","d");

IF((D2.0=="/")|(D2.0=="\")|(D2.1=="/")|(D2.1=="\")|(D2.2=="/")|(D2.2=="

\")|(D2.3=="/")|(D2.3=="\"))

QQ2=(~E2'&((D2.0&~SE0&~SE1)|(D2.1&SE0&~SE1)|(D2.2&~SE0&SE1)|(D2.3&S

E0&SE1))) (18,13,"d","d");

IF(E1'=="/")|(E1'=="\")|(E2'=="/")|(E2'=="\")

{QQ1=(~E1'&((D1.0&~SE0&~SE1)|(D1.1&SE0&~SE1)|(D1.2&~SE0&SE1)|(D1.3&

SE0&SE1))) (20,18,"d","d");

QQ2=(~E2'&((D2.0&~SE0&~SE1)|(D2.1&SE0&~SE1)|(D2.2&~SE0&SE1)|(D2.3&S

E0&SE1))) (20,18,"d","d");

} // выходные значения формируются путем составления логической

Q1'=~QQ1(0,0,"d","d"); // функции по функциональной схеме.(рис.2)

Q2'=~QQ2(0,0,"d","d");

}

|

Результаты логического моделирования узла

в пакете PCADбез учета реальных задержек.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.