Синтез комбинационной части на мультиплексорах заключается в следующем: на селектирующие входы мультиплексора подаются переменные, от которых зависят функции возбуждения триггеров, а на информационные логический ноль или логическая единица на каждый. При этом используются таблицы 5, 6, 7

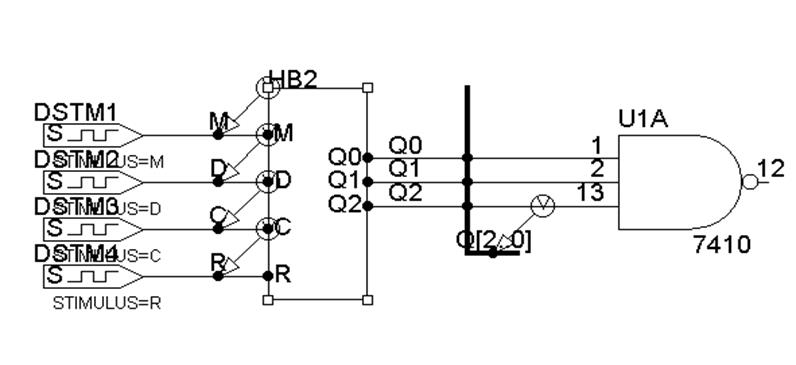

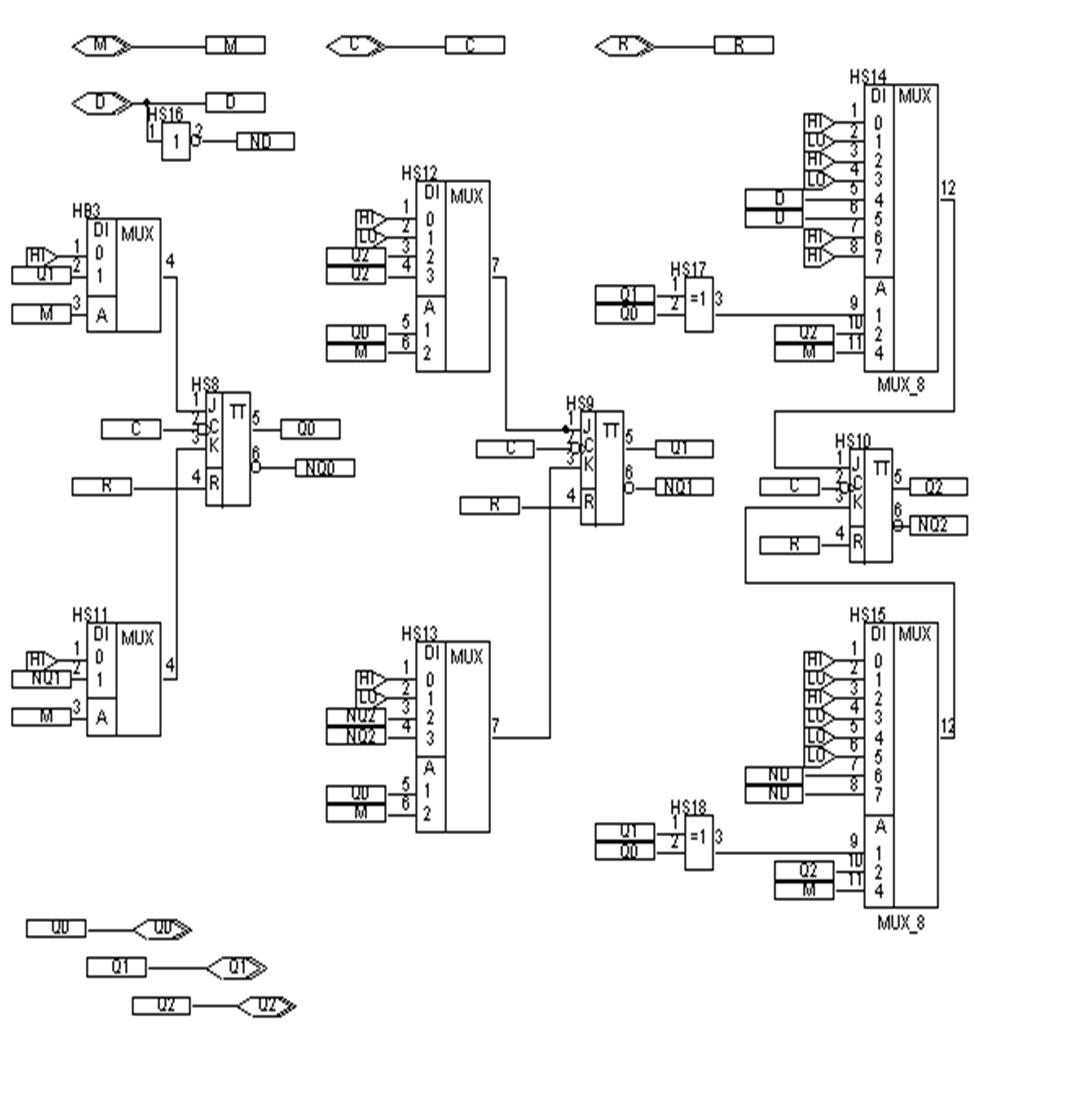

На рис 12 приведена схема верификации, а на рис. 13 схема замещения, построенная на мультиплексорах.

Рис.12

Рис.12

Рис13

Рис13

Результаты как на рис.4.

10. Синтез комбинационной части автомата на ПЗУ

Чтобы синтезироватькомбинационную часть в ПЗУ зашиваются таблицы 5, 6, 7, а на адресные входы подаются переменные, от которых зависят функции возбуждения триггеров.

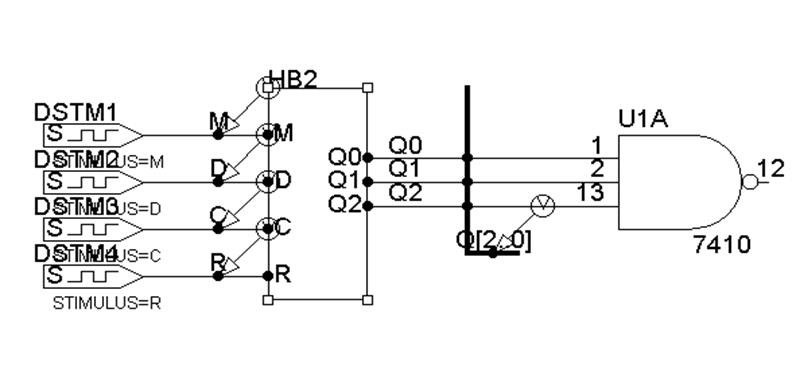

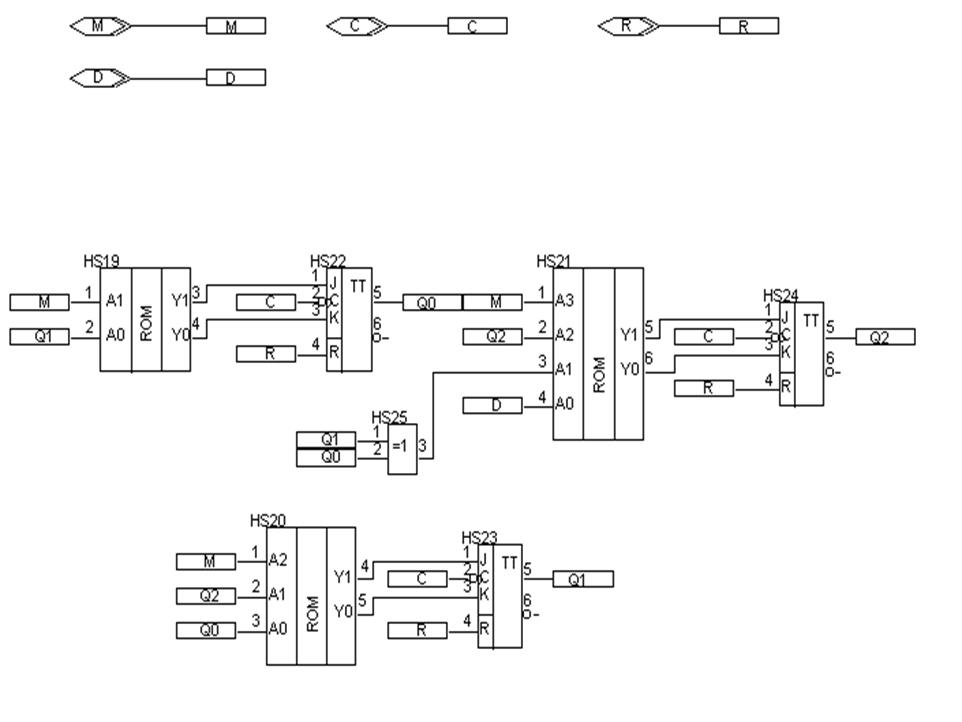

На рис. 14 приведена схема верификации, на рис. 15 схема замещения. Ниже приведены DSL-модели ПЗУ

ПЗУ на 2 входа, 2 выхода

PROCEDURE PZU_22 (

INPUT A1, A0 ;

OUTPUT Y1, Y0 ;

);

TRUTH_TABLE

[A1..A0]::[Y1,Y0];

0 :: 3 ;

1 :: 3 ;

2 :: 1;

3 :: 2 ;

END TRUTH_TABLE;

END PZU_22;

ПЗУ на 3 входа, 2 выхода

PROCEDURE PZU_32 (

INPUT A2, A1, A0 ;

OUTPUT Y1, Y0 ;

);

TRUTH_TABLE

[A2..A0] :: [Y1..Y0];

0 :: 3 ;

1 :: 0 ;

2 :: 3 ;

3 :: 0 ;

4 :: 1 ;

5 :: 1 ;

6 :: 2 ;

7 :: 2 ;

END TRUTH_TABLE;

END PZU_32;

ПЗУ на 4 входа, 2 выхода

PROCEDURE PZU_42 (

INPUT A3, A2, A1, A0 ;

OUTPUT Y1, Y0 ;

);

" TODO: add your DSL code below.

TRUTH_TABLE

[A3..A0] :: [Y1..Y0];

0 :: 3 ;

1 :: 3 ;

2 :: 0 ;

3 :: 0 ;

4 :: 3 ;

5 :: 3 ;

6 :: 0 ;

7 :: 0 ;

8 :: 0 ;

9 :: 2 ;

10 :: 0 ;

11 :: 2 ;

12 :: 3 ;

13 :: 2 ;

14 :: 3 ;

15 :: 2 ;

END TRUTH_TABLE;

END PZU_42;

Рис.14

Рис.14

Рис.15

Рис.15

11. Выводы, личные впечатления

В ходе выполнения работы были изучены методы синтеза и проектирования в пакете Design Lab 8 автоматов с памятью(вычитающего счетчика-регистра).

Данный пакет является современной системой моделирования, он имеет графический пользовательский интерфейс, позволяющий рисовать проектируемую схему(редактор Schematic) и временные диаграммы(Stimuls Editor), управляющая оболочка(Design Manager) из которой можно запускать все или большинство других программ пакета, не нужно это делать вручную. DesignLab8 поддерживают иерархическое проектирование, в этом мы тоже убедились при выполнении данной работы.

DesignLab8 содержит большое число графических и функциональных описаний компонентов в библиотеках, имеется возможность пользователю создавать свои библиотеки и компоненты, что является очень важным при проектировании схем с использованием отечественных компонентов, которые отсутствуют в стандартных библиотеках.

В пакете имеется встроенный внутренний язык DSL, с помощью которого можно описывать структурные, потковые и поведенческие модели.

В DesignLab8 имеется удобный постпроцессор моделирования Probe, который позволяет удобно просматривать и оценивать результаты моделирования, измерить задержки распространения сигналов.

В DesignLab8 имеется даже встроенный текстовый редактор.

При работе в DesignLab8, я столкнулась всего с несколькими моментами, которые меня разочаровали

Именно по работе по проектированию счетчика-регистра я сделала следующий вывод, что построение комбинационной схемы автомата с памятью на логических элементах не единственный способ, к тому же не является самым рациональным, из-за большего количества DSL-описаний. Наиболее мне понравился способ построения на ПЗУ.

В целом работа мне понравилась, она помогла закрепить знания, полученные в течение семестра.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.