NODE NM, ND, J0, K0, K1, J2, K2, J1, NQ0, NQ1, NQ2;

HS1:INV_DSL(M,NM);

HS2:INV_DSL(D,ND);

HS3:OR2_DSL(NM,Q1,J0);

HS4:OR2_DSL(NM,NQ1,K0);

HS5:JK_DSL(J0,C,K0,R,Q0,NQ0);

HS6:AND2_2_OR2_DSL(NM,NQ0,M,Q2,J1);

HS7:AND2_2_OR2_DSL(NM,NQ0,M,NQ2,K1);

HS8:JK_DSL(J1,C,K1,R,Q1,NQ1);

HS9:AND2_3_2_OR3_DSL(M,Q2,NM,NQ1,NQ0,M,D,J2);

HS10:AND3_3_OR2_DSL(NM,NQ1,NQ0,ND,M,Q2,K2);

HS11:JK_DSL(J2,C,K2,R,Q2,NQ2);

END MYCOUNTER;

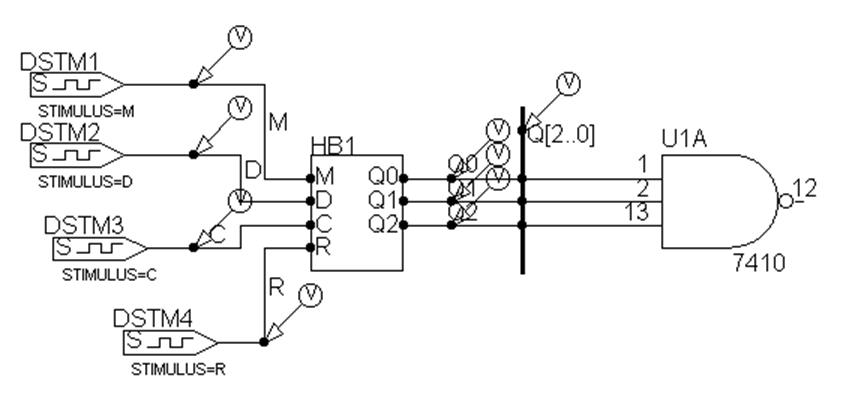

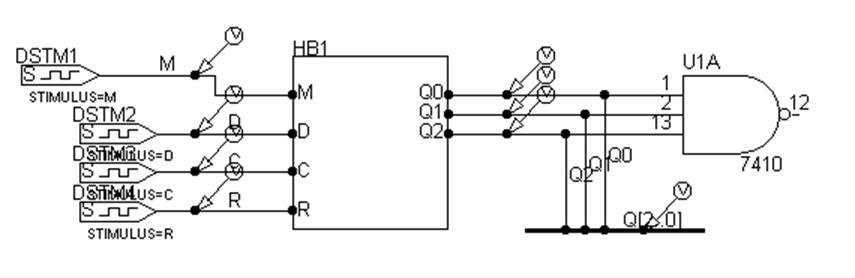

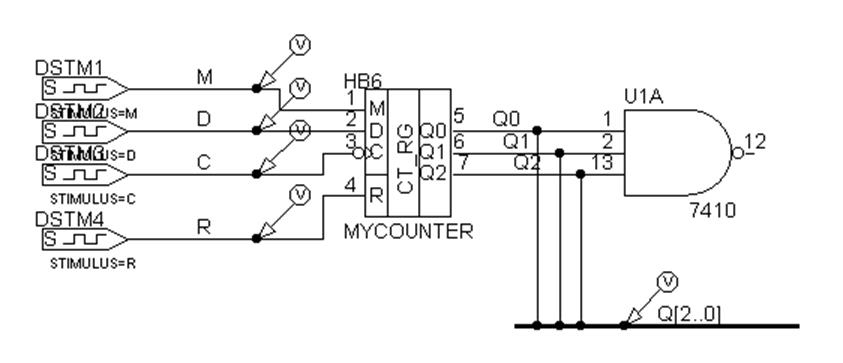

Схема верификации иерархического блока со структурной DSL-моделью представлена на рис. 3, а результат работы на рис. 4.

Рис. 3

Рис. 4

5. Проектирование иерархических символов для своей схемы.

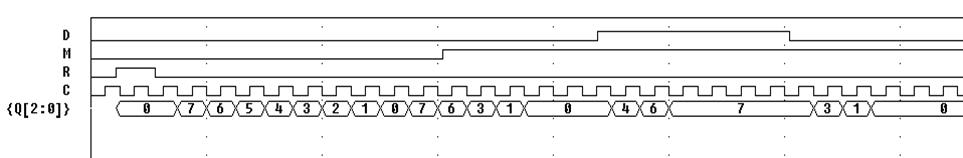

Ниже на рис. 5 представлены иерархические символы используемые для проектируемой схемы. А их DSL-модели были приведены при проектировании структурной DSL-модели.

Рис. 5

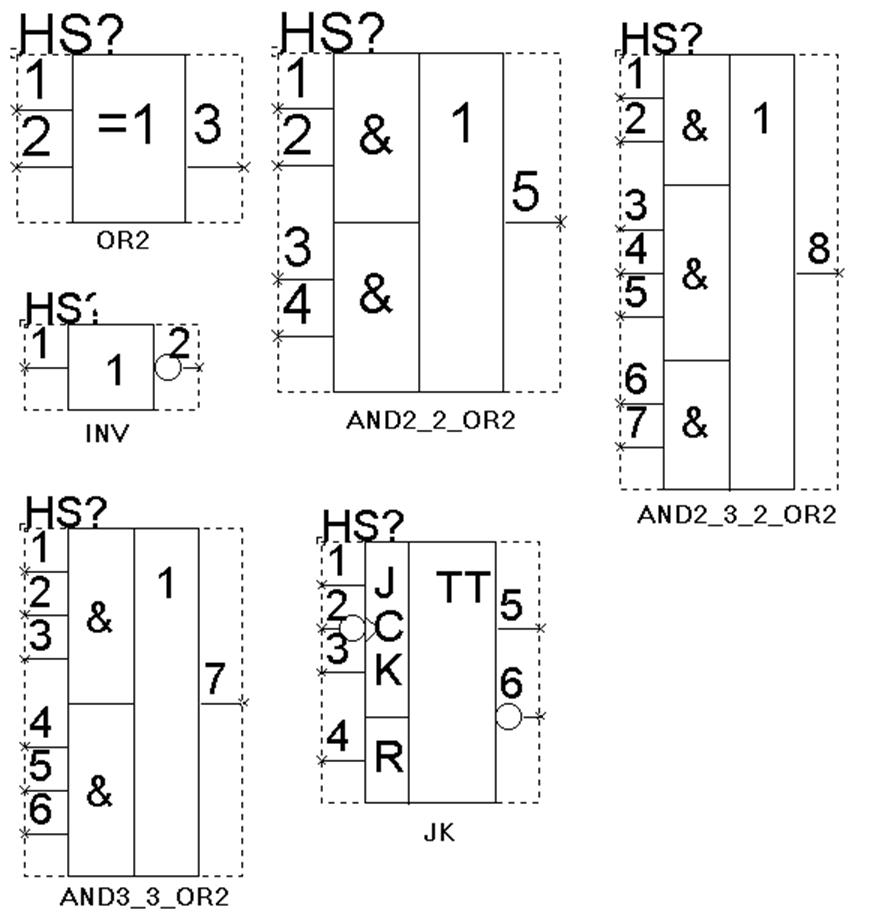

6. Проектирование иерархического блока со схемой замещения на ранее созданных иерархических символах.

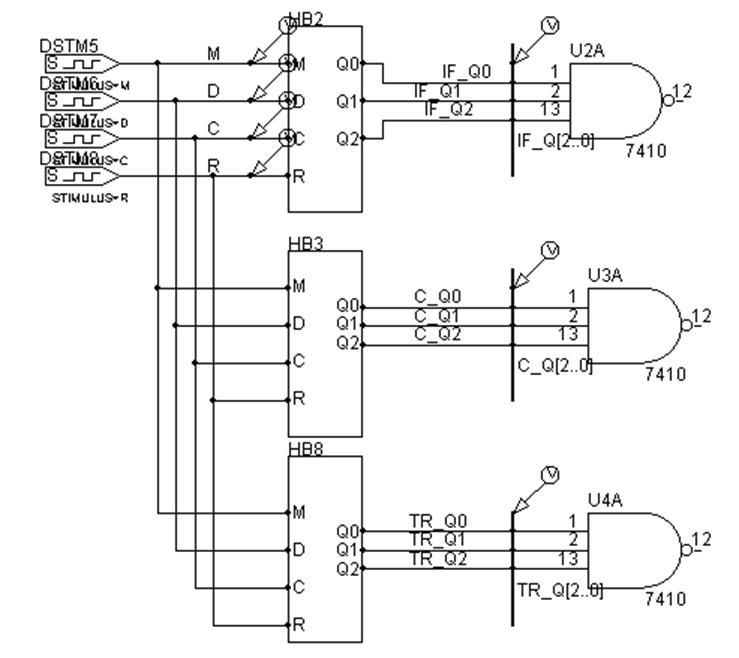

На рис. 6 представлена схема замещения на иерархических символах, на рисунке 7 – схема верификации, а на рисунке 8 – результаты работы.

Рис.6

Рис.7

Рис.8

7. Поведенческая DSL-модель цифрового автомата с любой комбинацией операторов.

Ниже приведен текст поведенческих DSL-моделей (все комбинации операторов).

PROCEDURE IF_DSL (

INPUT M, D, C, R ;

OUTPUT Q0, Q1, Q2 CLOCKED_BY /C RESET_BY R;

);

IF M = 0 THEN [Q2..Q0] = [Q2..Q0].-.1;

ELSE [Q2..Q0] = [D,Q2,Q1];

END IF;

END IF_DSL;

PROCEDURE C_DSL (

INPUT M, D, C, R ;

OUTPUT Q0, Q1, Q2 CLOCKED_BY /C RESET_BY R ;

);

CASE M

WHEN 0 => [Q2..Q0] = [Q2..Q0].-.1;

WHEN 1 => [Q2..Q0] = [D,Q2,Q1];

END CASE;

END C_DSL;

PROCEDURE TR_DSL (

INPUT M, D, C, R ;

OUTPUT Q0, Q1, Q2 CLOCKED_BY /C RESET_BY R;

);

TRUTH_TABLE

M :: [Q2..Q0];

0 :: [Q2..Q0].-.1;

1 :: [D,Q2,Q1];

END TRUTH_TABLE;

END TR_DSL;

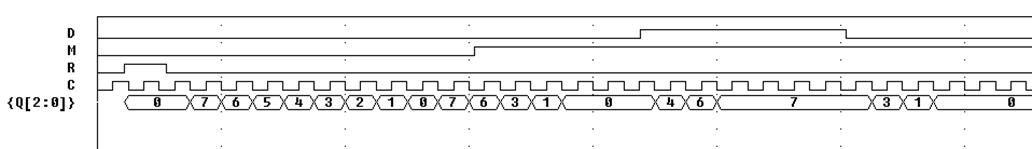

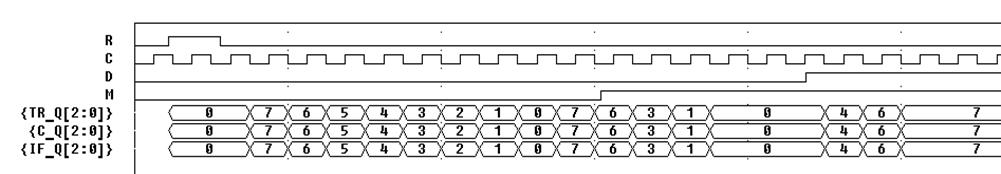

На рис.9 приведена схема верификации, а на рис. 10 результаты работы.

Рис. 9

Рис. 10

8. Потоковая DSL-модель автомата

Ниже приведен текст потоковой DSL-модели. На рис. 11 приведена схема верификации. Иерархический блок преобразован в иерархический символ.

PROCEDURE POTOK (

INPUT M, D, C, R ;

OUTPUT Q0, Q1, Q2 ;

);

JK_FLOP TT0, TT1, TT2 CLOCKED_BY /C RESET_BY R;

TT0.J= (/M)+(Q1);

TT0.K= (/M)+(/Q1);

Q0 = TT0;

TT1.J= ((/M)*(/Q0))+(M*Q2);

TT1.K= ((/M)*(/Q0))+(M*(/Q2));

Q1 = TT1;

TT2.J= (M*Q2)+((/M)*(/Q1)*(/Q0))+(M*D);

TT2.K=((/M)*(/Q1)*(/Q0))+(M*Q2*(/D));

Q2 = TT2;

END POTOK;

Рис. 11

Результаты такие же как и на рис. 4.

9. Синтез комбинационной части автомата на мультиплексорах

В этой части работы использованы три типа мультиплексоров: 2 в 1, 4 в 1, 8 в 1. Их УГО можно увидеть на рис. 12, DSL-модели приведены ниже.

PROCEDURE MUX_2 (

INPUT IN0, IN1, A ;

OUTPUT OUT ;

);

TRUTH_TABLE

A :: OUT;

0 :: IN0;

1 :: IN1;

END TRUTH_TABLE;

END MUX_2;

PROCEDURE MUX_4 (

INPUT IN0, IN1, IN2, IN3, A0, A1 ;

OUTPUT OUT ;

);

TRUTH_TABLE

[A1..A0] :: OUT;

0 :: IN0;

1 :: IN1;

2 :: IN2;

3 :: IN3;

END TRUTH_TABLE;

" TODO: add your DSL code below.

END MUX_4;

PROCEDURE MUX_8 (

INPUT IN0, IN1, IN2, IN3, IN4, IN5, IN6, IN7, A0, A1, A2 ;

OUTPUT OUT ;

);

" TODO: add your DSL code below.

TRUTH_TABLE

[A2..A0] :: OUT;

0 :: IN0;

1 :: IN1;

2 :: IN2;

3 :: IN3;

4 :: IN4;

5 :: IN5;

6 :: IN6;

7 :: IN7;

END TRUTH_TABLE;

END MUX_8;

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.