Программа выполнения лабораторной работы 3

в САПР XilinxISE6.2 и Active-HDL7.1

Цель работы - научиться выполнять процедуры синтеза, реализации и временного моделирования цифровых устройств в САПР XilinxISE 6.2и САПР Active-HDL7.1:

· Закрепить технологию функционального моделирования в среде DesignFlowManagerпакета Active-HDL 7.1;

· Познакомиться с современными инструментами синтеза и реализации цифровой аппаратуры;

· Познакомиться с программой ChipViewer – графической формой представления заключительного отчёта о выполненных процедурах синтеза и реализации проекта для конкретной ПЛИС.

· Освоить процедуру временного моделирования Timing Simulation с передачей данных из одной САПР в другую (из Xilinx ISE 6.2 в Active-HDL 7.1);

Перед началом работы загрузите в среду проектирования Active-HDL 7.1 своё рабочее пространство, созданное на первой лабораторной работе, и сделайте активным проект Lab3. В нём должны находиться все три варианта описания вашего цифрового автомата (VHDL – модель, схема и диаграмма состояний).

Убедитесь, что все исходные файлы сохранились. Надёжнее всего восстановить результаты первой и второй работы с твёрдого носителя, используя команды пакета ArchiveWorkspace и RestoreWorkspace из выпадающего меню Workspace.

ЗАДАНИЕ 1. Закрепление технологии функционального моделирования в среде DesignFlowManagerпакета Active-HDL 7.1.

Ориентировочное время выполнения задания – 15 мин. (0,5 балла).

Это задание выполняют только те студенты, которые не успели закончить лабораторную работу 2 (задание 4).

1.1. Создайте в своём рабочем пространстве новый проект Lab3 и добавьте в него из проекта Lab1 (первая лабораторная работа) исходные файлы с моделями разработанных вами элементов и триггеров (в нашем примере and2_my.vhd, xor_my.vhd, inv_my.vhd, dff_my.vhd). При выполнении данной операции установите флажок Makelocalcopy, чтобы сделать в новом проекте локальные копии, а не ссылки.

Добавьте сюда же схемное описание разработанного цифрового узла на ваших элементах, то есть файл count5_BDE_my.bde.

1.2. Из проекта Lab2 добавьте ещё два файла: диаграмму состояний (файл count5_FSM.adf) и описание узла на языке VHDL (файл count5_HDE.vhd). Теперь у вас есть три варианта представления проекта: код на языке VHDL, схема и диаграмма состояний. Откомпилируйте все полученные файлы.

1.3. Активизируйте закладку designflow manager и нажмите кнопку options (рис.1) рядом с пиктограммой functionalsimulation.

Рис.1. Устанавливаем опции для функционального моделирования

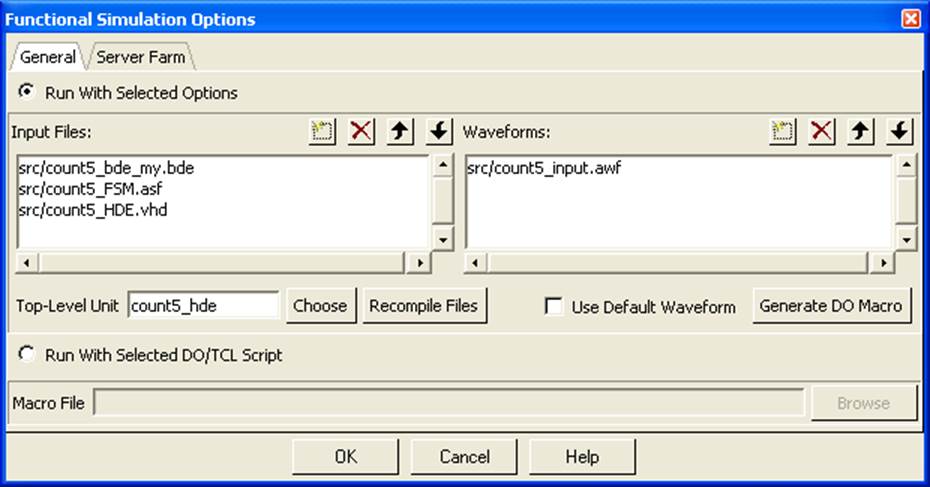

На открывшейся диалоговой панели FunctionalSimulationOptions сделайте установки, как показано на рис.2. Если у вас не было файла с временными диаграммами входных сигналов count5_input.awf, то создайте его. В поле Top-LevelUnit поочерёдно задавайте имя модуля верхнего уровня, чтобы промоделировать все три варианта вашего проекта на одном и том же наборе входных сигналов.

Рис.2. Диалоговая панель установок для выполнения функционального моделирования

Учтите, что нажатие на кнопку functionalsimulation (см. справа) не выполняет моделирование, а только

инициализирует его. Убедитесь, что все варианты описания проекта соответствует

заданию, и показывают правильные реакции на внешние воздействия.

Учтите, что нажатие на кнопку functionalsimulation (см. справа) не выполняет моделирование, а только

инициализирует его. Убедитесь, что все варианты описания проекта соответствует

заданию, и показывают правильные реакции на внешние воздействия.

Сводную временную диаграмму сохраните в файле count5_all.awf, чтобы показать её преподавателю.

Теперь всё готово для того, чтобы приступить к третьей лабораторной работе.

ЗАДАНИЕ 2. Синтез и реализация цифровых устройств. Ориентировочное время выполнения задания – 45 мин. (1 балл).

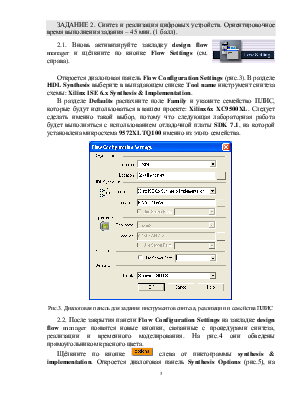

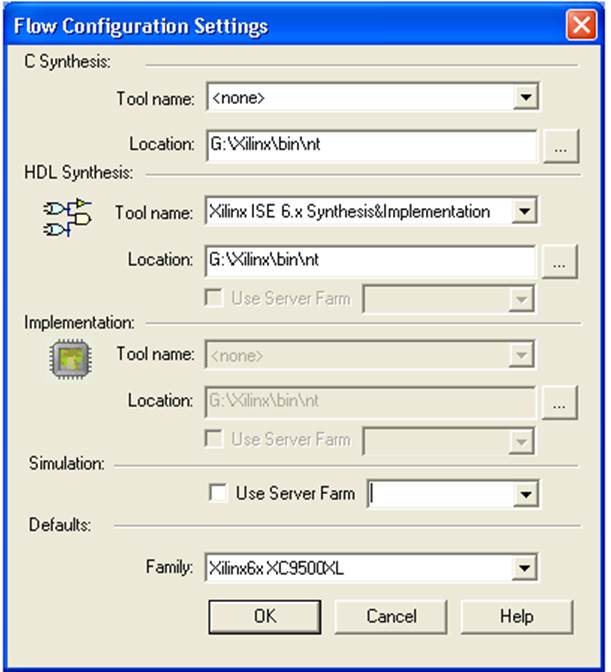

2.1. Вновь активизируйте закладку designflow manager и щёлкните по кнопке Flow Settings(см. справа).

Откроется диалоговая панель FlowConfigurationSettings(рис.3). В разделе HDLSynthesis выберите в выпадающем списке Tool name инструмент синтеза схемы: Xilinx ISE 6.x Synthesis & Implementation.

В разделе Defaults распахните поле Family и укажите семейство ПЛИС, которые будут использоваться в вашем проекте: Xilinx6xXC9500XL. Следует сделать именно такой выбор, потому что следующая лабораторная работа будет выполняться с использованием отладочной платы SDK 7.1, на которой установлена микросхема 9572XLTQ100 именно из этого семейства.

Рис.3. Диалоговая панель для задания инструментов синтеза, реализации и семейства ПЛИС

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.