3.5. Измерьте на временных диаграммах в окне редактора WaveformEditorзадержки распространения сигналов от внешних входов (например, от C и R) до внешних выходов (например, до Q0, Q1 и Q2).

Сравните измеренные значения с аналогичными величинами, ранее полученными в задании 2 (TimingReport).

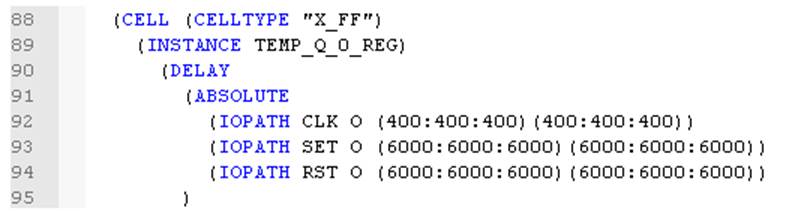

3.6. Откройте текстовый файл count5_hde_timesim.sdf со стандартными задержками. На рис.13 показан фрагмент такого файла.

Рис.13. Фрагмент SDF – файла с указанием задержек для D – триггера (“X_FF”)

Здесь описываются задержки для триггера «X_FF», точнее для его конкретного экземпляра (instance) TEMP_Q_0_REG. Задержки задаются отдельно для каждого входа триггера: CLK – входа тактирования, SET – входа установки триггера в “1’ и RST – входа сброса триггера в ‘0’.

Первые три числа в круглых скобках (400:400:400) задают минимальную, среднюю и максимальную задержки при переключении выхода триггера из ‘0’ в ‘1’. Следующие три числа в круглых скобках характеризуют те же задержки при переключении выхода триггера в обратном направлении, то есть из ‘1’ в ‘0’. Величины задержек задаются в пикосекундах.

Увеличьте задержку по входу синхронизации CLK на 1ns и по входу сброса на 2ns. Убедитесь, что при повторном моделировании эти изменения отражаются на временных диаграммах.

Измените положение переключателя SDFType(см. рис.12), чтобы выяснить, учитывается ли при временном моделировании характер задаваемых задержек (Minimum, Typical, Maximum). Чтобы эксперимент был результативным, сделайте максимальные задержки отличными от типичных.

3.7. Вновь откройте диалоговую панель SynthesisOptions и в поле SpeedGrade задайте другой уровень быстродействия: например, вместо значения -5 поставьте значение -10. Повторите все ранее выполненные процедуры синтеза, реализации и временного моделирования. Снова измерьте задержки от тех же входов до тех же выходов. Убедитесь в том, что они стали больше. Занесите результаты описанных экспериментов в сводную таблицу задержек.

3.8. Проделайте описанную выше работу для второго и третьего вариантов описания своего проекта – в виде цифрового автомата и схемы. Сравните полученные результаты. Сделайте соответствующие выводы.

3.9. Составьте сводную таблицу, в которой для каждого промоделированного варианта, полученного процедурами синтеза и реализации, приводятся измеренные значения задержек распространения сигналов.

ЗАДАНИЕ 4. Исследование результатов проектирования с помощью программы ChipViewer. Ориентировочное время выполнения задания – 45 минут (1 балл).

4.1. Выполнив синтез и реализацию своего проекта, запустите процедуру ViewFittedDesign (ChipViewer), чтобы посмотреть результаты размещения и трассировки элементов схемы на кристалле в графическом формате. С помощью этого инструмента Вы можете исследовать входы и выходы, детальное описание макроячеек ПЛИС, синтезированные булевские уравнения и назначения контактов.

4.2. Исследуйте возможности программы ChipViewer, созданной дляпросмотра кристалла: выполните экспертизу входных и выходных сигналов, проследите за связями между макроячейками.

Вызовите детальную информацию о каждой макроячейке: список её сигналов, реализованные ячейкой булевские уравнения, схемное описание макроячейки.

4.3. Познакомьтесь с конструкторским описанием используемой ПЛИС: видом сверху и видом снизу, убедитесь, что все заданные вами порты проекта верхнего уровня выведены на внешние контакты микросхемы.

4.4. Исследуйте возможности временного анализатора TimingAnalyzer. Определите с его помощью временные задержки от внешних входов до внешних выходов.

ЗАДАНИЕ 4. Исследование предельные возможности ПЛИС, смонтированной на отладочной плате SDK 7.1.

Ориентировочное время выполнения задания – 15 мин. (0,5 балла).

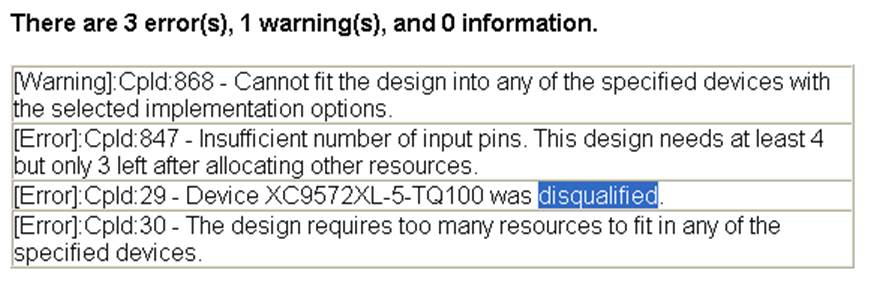

Придумайте проект, которому требуется ресурсов больше, чем имеется в ПЛИС xc9572xlTQ100. Проведите эксперимент, подтверждающий невозможность реализации своего проекта в имеющейся микросхеме.

Не может выполнить операции размещения и трассировки проекта в любое из указанных устройств (ПЛИС) с заданными опциями реализации.

Недостаточное число входных контактов. Этот проект нуждается по крайней мере в 4 контактах, но имеется только 3 левых контакта после распределения других ресурсов.

Устройство XC9572XL-5-TQ100 не пригодно для данного проекта.

Проект требует слишком большого количества ресурсов, чтобы реализовать специфицированный проект.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.