Проделайте то же самое и для третьего способа описания проекта в виде блок – схемы. Сравните полученные результаты по количеству оборудования.

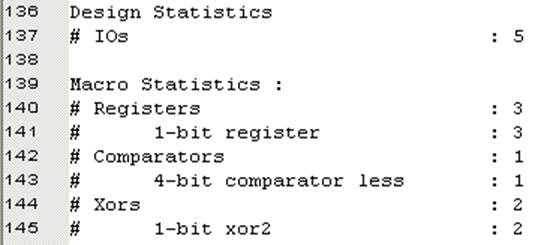

2.6. Вернитесь к первому варианту описания своего проекта в виде VHDL-модели. Активизируйте процесс ViewSynthesisReport, чтобы посмотреть отчёт о результатах синтеза в текстовом формате. Фрагмент такого отчёта показан на рис.8. Убедитесь, что номенклатура и число логических элементов в нём совпадают с автоматически сгенерированной схемой. В случае если обнаружится несовпадение, постарайтесь пояснить причины различия в этих отчётах.

Рис.8. Текстовая форма представления отчёта о результатах синтеза (фрагмент)

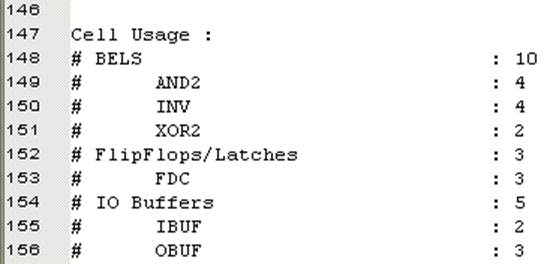

2.7. Исполните процедуру FitterReport, чтобы посмотреть результаты реализации вашего проекта (так называются операции размещения и трассировки). Фрагмент такого отчёта, созданный в формате HTML, показан на рис. 9.

Откройте поочерёдно все пункты меню FitterReport и изучите представленную в них информацию. Сравните приведённые в разделе Equation функции возбуждения триггеров с теми, что вы получили на картах Карно в процессе ручного синтеза схемы (или с помощью программы CarnoMinimizer).

Оцените в процентном отношении использованные в ПЛИС ресурсы.

Посмотрите, какие контакты микросхемы XC9572XL выбраны системой для входных C, Rи выходных Q0, Q1, Q2 сигналов.

При отсутствии USF-файла, в котором явно задаётся эта информация, система сама решает, как ей удобнее составить расписание выводов ПЛИС.

Рис.9. Фрагмент отчёта о результатах реализации проекта в кристалле ПЛИС

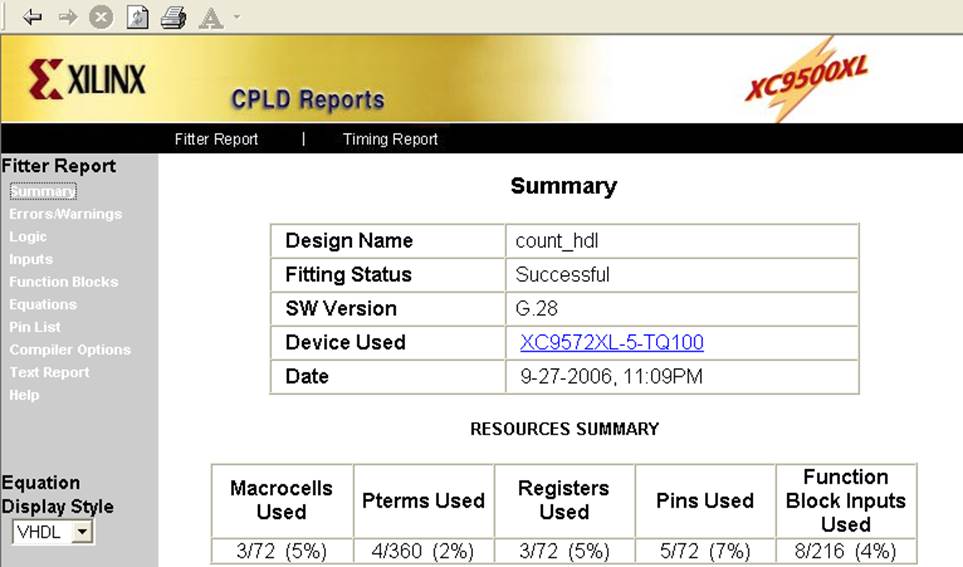

2.8. Активизируйте раздел TimingReport. Фрагмент отчёта о временных параметрах синтезированной схемы представлен на рис.10. Просмотрите отдельные пункты этого отчёта.

Оцените величины задержек, время предустановки данных на входах триггеров, максимальное быстродействие синтезированной схемы.

Рис.10. Отчёт о временных параметрах, полученных в результате реализации проекта

в ПЛИС XC9572XL -5 (3.0) (фрагмент)

ЗАДАНИЕ 3. Исследование особенностей временного моделирования, выполняемого после синтеза и реализации проекта. Ориентировочное время выполнения задания – 60 мин. (2 балла).

3.1. Найдите в дереве процессов (см. рис.6) пункт ImplementDesign, распахните раздел OptionalImplementationTools и запустите в нём процедуру GeneratePost-FitSimulationModel.

3.2. Щёлкните два раза на строке Post-FitSimulationModelReport, чтобы открыть текстовый отчёт о проделанной процедуре. Убедитесь, что в нём имеются записи:

![]()

свидетельствующие о том, что созданы два файла, необходимые для выполнения временного моделирования.

Первый файл с расширением *.vhd представляет собой структурную VHDL-модель вашего проекта, реализованную на уровне ресурсов выбранного кристалла ПЛИС. В ней используются модели элементов из библиотеки SimPrimLibrary, учитывающие задержки распространения сигналов.

Величины этих задержек находятся в соответствующих файлах, имеющих стандартный формат SDF (StandardDelayFormat). Этим и объясняется расширение второго файла, сгенерированного системой. В данном примере он называется count5_hde_timesim.sdf.

Оба файла генерируются системой автоматически и помещаются в директорию synthesis вашего проекта. Познакомьтесь с содержимым каждого файла.

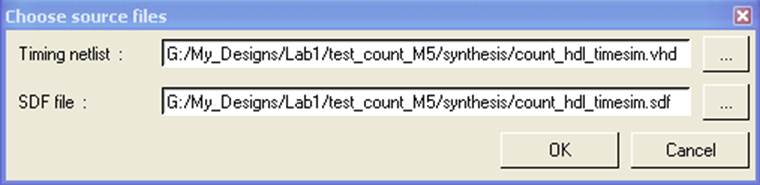

3.3. Перейдите в интегрированную среду пакета Active-HDL 7.1 и

щёлкните на кнопке ![]() ,

находящейся на закладке designflow (см.

рис.4). В появившемся диалоговом окне Chousesourcefiles (рис.11)

в поля Timingnetlist и SDFfile введите

соответствующие файлы. Делается это очень просто, так как они видны по

умолчанию. Достаточно лишь нажать на кнопке обзора

,

находящейся на закладке designflow (см.

рис.4). В появившемся диалоговом окне Chousesourcefiles (рис.11)

в поля Timingnetlist и SDFfile введите

соответствующие файлы. Делается это очень просто, так как они видны по

умолчанию. Достаточно лишь нажать на кнопке обзора ![]() .

.

Рис.11. Задаём ссылки на два файла (*.vhd и *.sdf), в которых хранятся данные,

необходимые для выполнения временного моделирования

После закрытия панели Chousesourcefiles в окне DesignBrowser пакета Active-HDL 7.1 появится папка timing со ссылками на эти файлы.

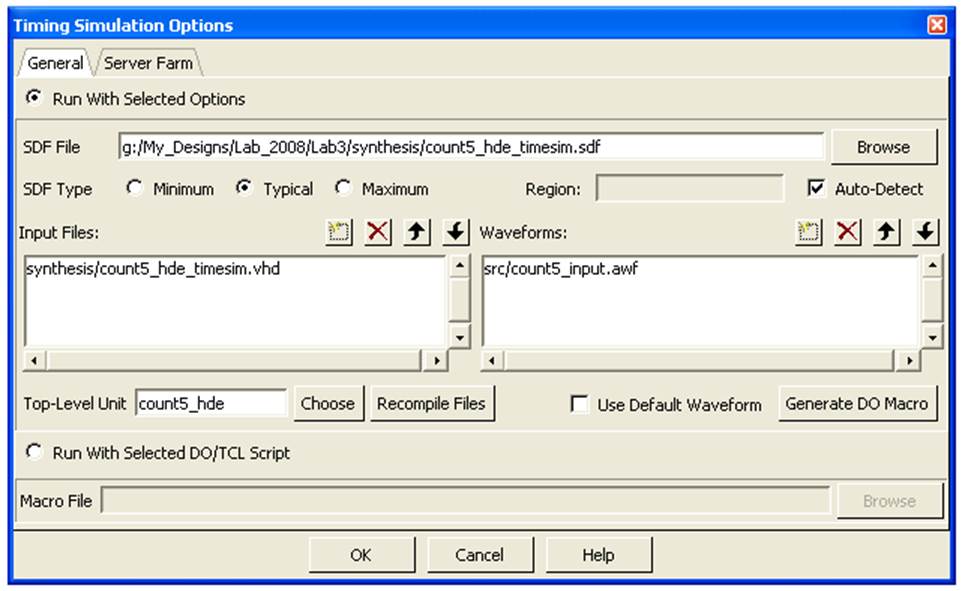

3.4. Настройте временное моделирование, нажав на

кнопку ![]() рядом с

пиктограммой timingsimulation (см. рис.4).

рядом с

пиктограммой timingsimulation (см. рис.4).

На экране монитора появится диалоговая панель TimingSimulationOptions, на которой надо установить параметры в соответствии с рис.12.

Рис.12. Настраиваем параметры временного моделирования

Обратите внимание, в данном эксперименте предлагается использовать тот же файл count5_input.awf с диаграммами входных сигналов, что и для функционального моделирования.

Закройте диалоговую панель и выполните временное моделирование,

нажав на пиктограмму timingsimulation (см. справа).

Закройте диалоговую панель и выполните временное моделирование,

нажав на пиктограмму timingsimulation (см. справа).

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.