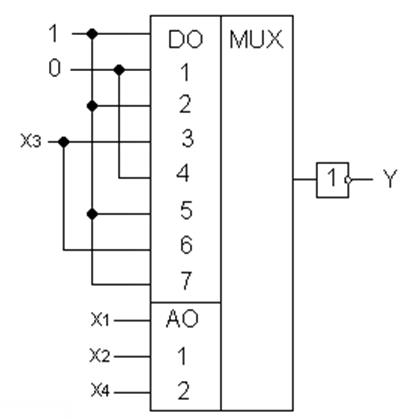

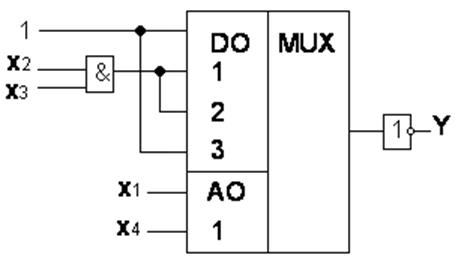

Рисунок 2.2 - Мультиплексор 8:1(кількість адресних входів 3)

2) Виключимо х2х3

(x1 x4; ![]()

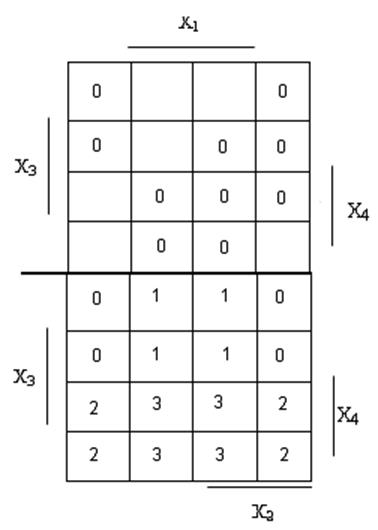

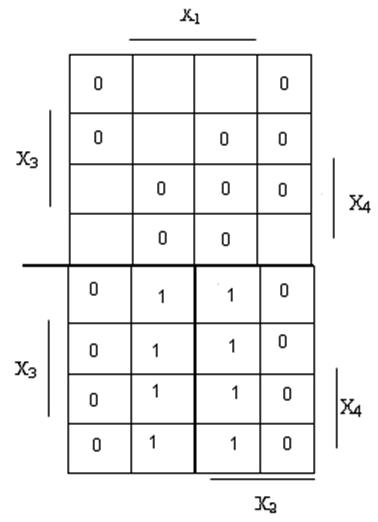

Розбиваємо діаграму на 4 піддіаграм (4:1):

Визначаємо функції входів мультиплексора від неприєднаних змінних до адресних змінних (х2х3) шляхом порівняння піддіаграм з діаграмою:

Рисунок 2.3– Мультиплексор 4:1(кількість адресних входів 2)

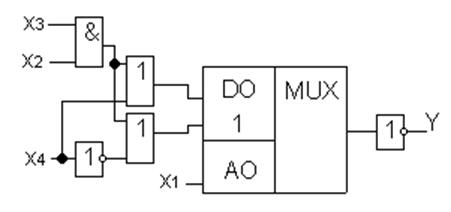

3) Виключимо х2х3х4

(x1; ![]()

Розбиваємо діаграму на 2 піддіаграм (2:1):

Визначаємо функції входів мультиплексора від неприєднаних змінних до адресних змінних (х2х3х4) шляхом порівняння піддіаграм

Рисунок 2.4– Мультиплексор 2:1(кількість адресних входів 1)

Реалізація даного мультиплексора буде досить складною, порівняно з попередніми. На мою думку, найпростішою реалізацією мультиплексора являється мультиплексор, зображений на рисунку 2.2, бо він вимагає найменшої кількості корпусів. Якщо є необхідність скоротити розрядність даного елемента, на якому реалізується обрана функція, можна скористатись рисунками 2.3.

2.2 Виконати автоматичне проектування пристрою за п. 2.1 (на ВІС програмованої структури родини MAX7000S) на рівні макро- та/або мегафункцій у графічному редакторі Quartus II. Навести потрібні файли проекту із зазначенням його імені з варіантом XX та дати стисле тлумачення результатів, порівняти їх з результатами проектування вручну за п. 2.1.

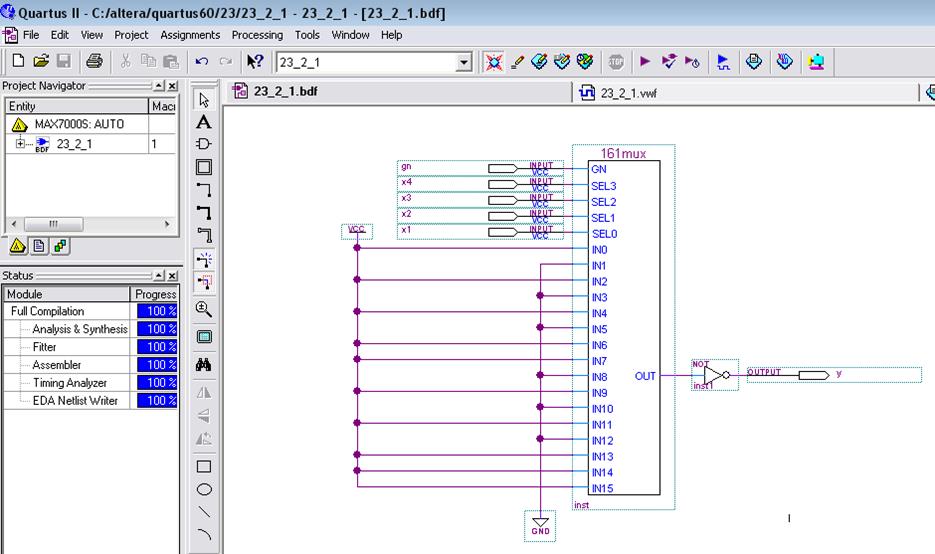

Рисунок 2.5 - Мультиплексор 16:1

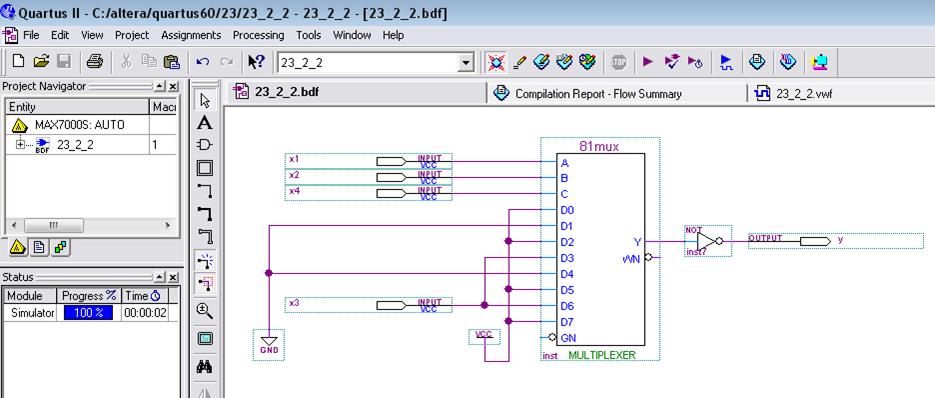

Рисунок 2.6 - Мультиплексор 8:1

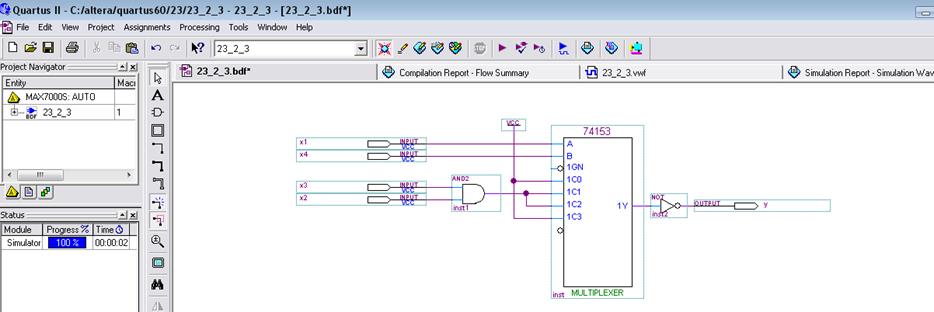

Рисунок 2.7 - Мультиплексор 4:1

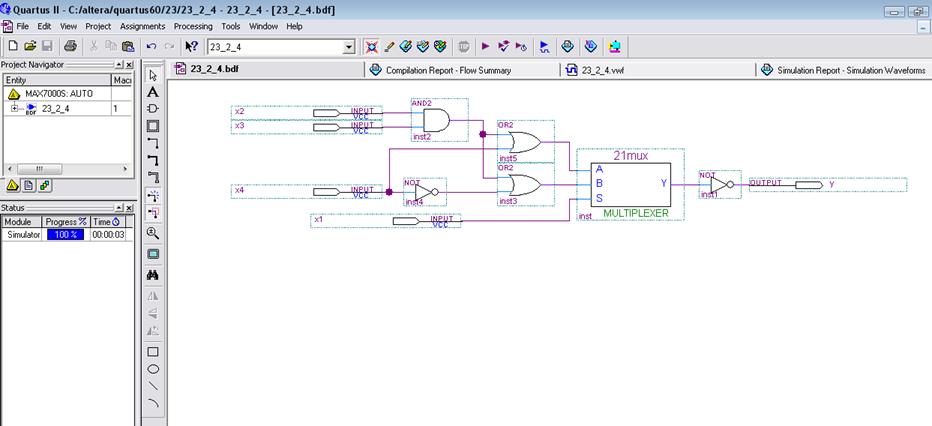

Рисунок 2.8 – Мультиплексор 2:1

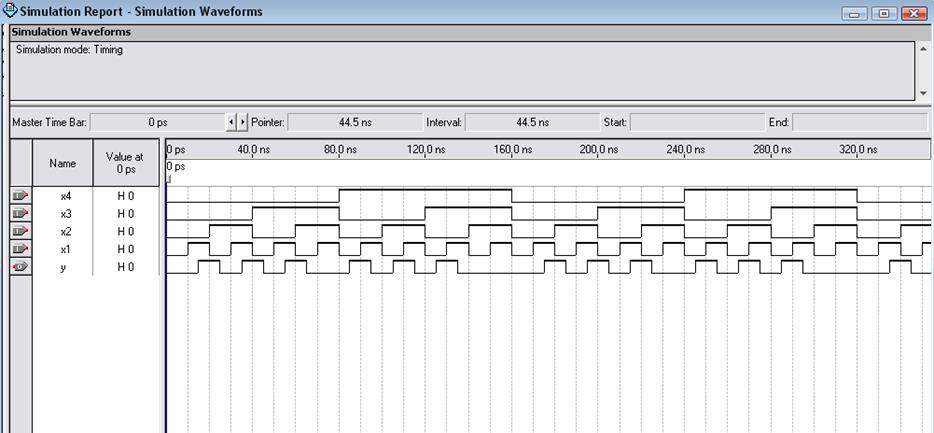

Часові діаграми мультиплексора:

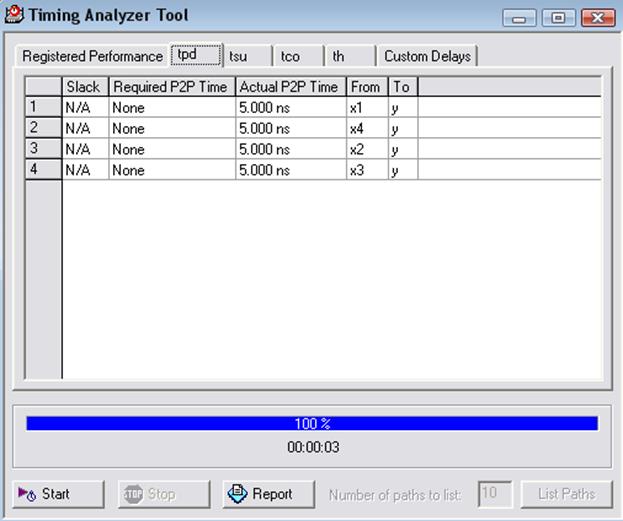

Часовий аналіз виконаний за допомогою матриці затримок:

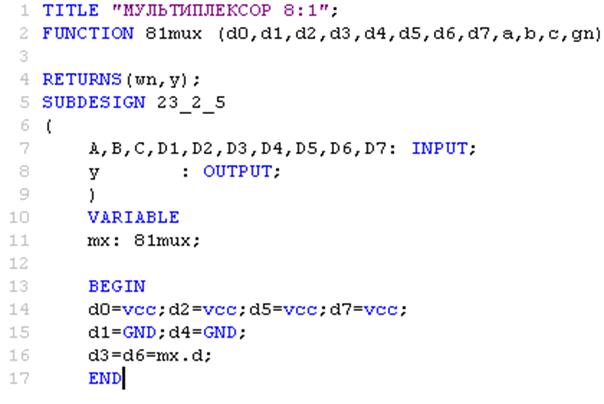

2.3 Виконати п. 2.2 на тому самому або вищому структурному рівні у текстовому редакторі Quartus II (з іншою назвою проекту, що містить варіант XX).

Автоматичне проектування у текстовому редакторі Quartus II виконане на мультиплексорі 8:1.

Часові діаграми даного мультиплексора (створеному у текстовому редакторі) повністю співпадають з результатами отриманими після компілювання схем у графічному редакторі та отриманих їх часових діаграм.

Отже, можна зробити висновок, що дані мультиплексори спроектовано вірно.

Висновки: в даному пункті було побудовано цифровий комбінаційний пристрій, що виконує функцію комутування.

3 Спроектувати пристрій на ЦПП

3.1-3.2 - Згідно з варіантом синтезувати пристрій (Реверсивний розподільник імпульсів і рівнів на регістрі зсуву, на кількість каналів К=8) на основі заданої елементної бази (ІС жорсткої структури). Виконати аналіз функціонування пристрою та довести його самовідновність. Навести повну таблицю перемикання (за необхідністю), повний перемикальний граф.

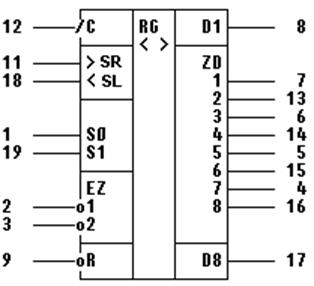

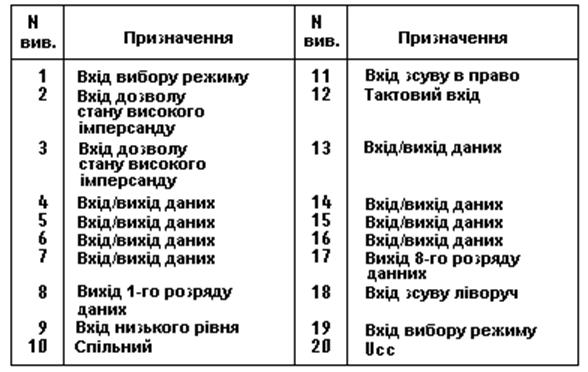

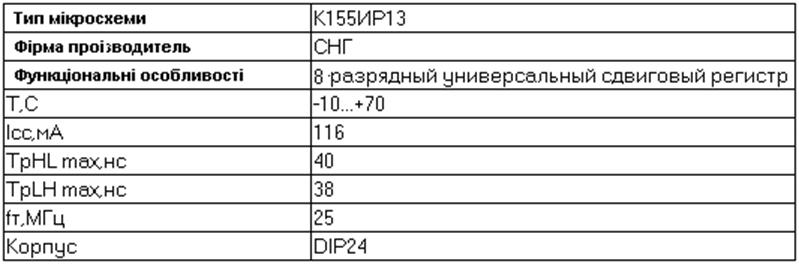

Для реалізації даного завдання, вибираємо найбільш ходову мікросхему 8-розрядного універсального регістра зсуву, серії К155ИР13. Нам доведеться використати дві таких мікросхеми:

Функціональна схема мікросхеми К155ИР13 (Uжив=5 В)

Таблиця – параметри мікросхеми К155ИР13:

В даній мікросхемі синхронна паралельне завантаження здійснюється шляхом встановлення напруги висого рівня на управляючі входи S0, S1. На об’єднані входи/виходи, які знаходяться у стані високого імперсанда подається восьми розрядне слово,яке по положенні фронту на C записується в тригери.

Зсув праворуч здійснюється синхронно з приходом додатного фронту тактового імпульса на С при установці на S0 високого, а на S1 низького рівня. В цьому режимі дані послідовно зчитуються з входу SR. Зсув ліворуч здійснюється синхронно з приходом додатного фронту тактового імпульсу на С при установці на S0 низького, а на S1 високого рівня. В цьому режимі данні послідовно зчитуються з входу SL.

Режим блокування реалізується при подачі на обидва управляючих входи S0, S1 напруги низького рівня.

Реалізація варіанту завдання на мікросхемах К155ИР13

Так як нам необхідно отримати реверсивний розподільник імпульсів і рівнів на регістрі зсуву, на кількість каналів К=8, подамо на входи регістра комбінацію 00000001 (один рівень), який в подальшому при кожному додатньому фронту тактового синхроімпульсу буде переміщатись в залежності від вхідних рівнів на входах S0 та S1.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.