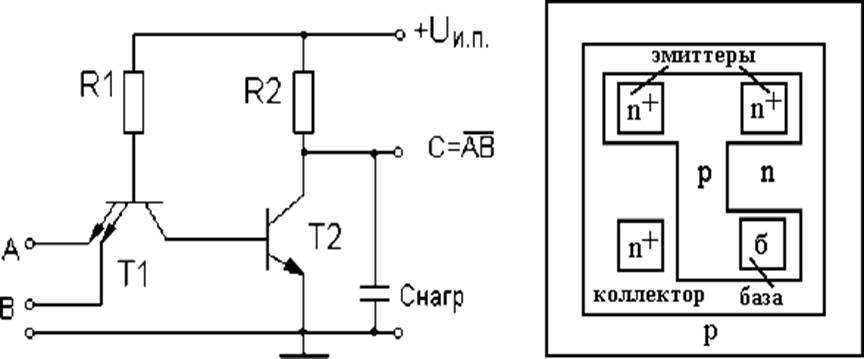

Пусть на один из входов МЭТ подано напряжение низкого уровня (логического нуля), тогда напряжение на базе МЭТ снизится до напряжения открытого р-n+ перехода (≈ 0.8 вольта). Это напряжение при передаче на базу транзистора Т2 распределяется между двумя последовательно включёнными р-n переходами (диодом, образованным расширенной областью базы и коллекторным слоем транзистора Т1, и эмиттерным переходом транзистора Т2. И тогда напряжение на базе Т2 будет таким, при котором транзистор Т2 будет закрыт. На выходе логического элемента - высокий уровень напряжения (логическая единица).

Если на оба входа подаётся напряжение, при котором переходы эмиттер-база закрываются, на базе МЭТ обеспечивается такой уровень напряжения, при котором открывается переход коллектор-база (инверсное включение МЭТ).

Ток в цепи коллектора МЭТ равен Iк=(Uип-Uбэ(нас)-Uбк) / R1. Транзистор Т2 при этом открывается, и на выходе ЛЭ обеспечивается низкий уровень сигнала (логический ноль).

|

а б

Рис.11. Схема простейшего элемента ТТЛ логики (а);

топология МЭТ транзистора (б)

Для ТТЛ элементов уровень входного напряжения, при котором транзистор Т1 закрывается по переходу база-эмиттер, равен или больше 2.4 вольта, что является уровнем логической единицы.

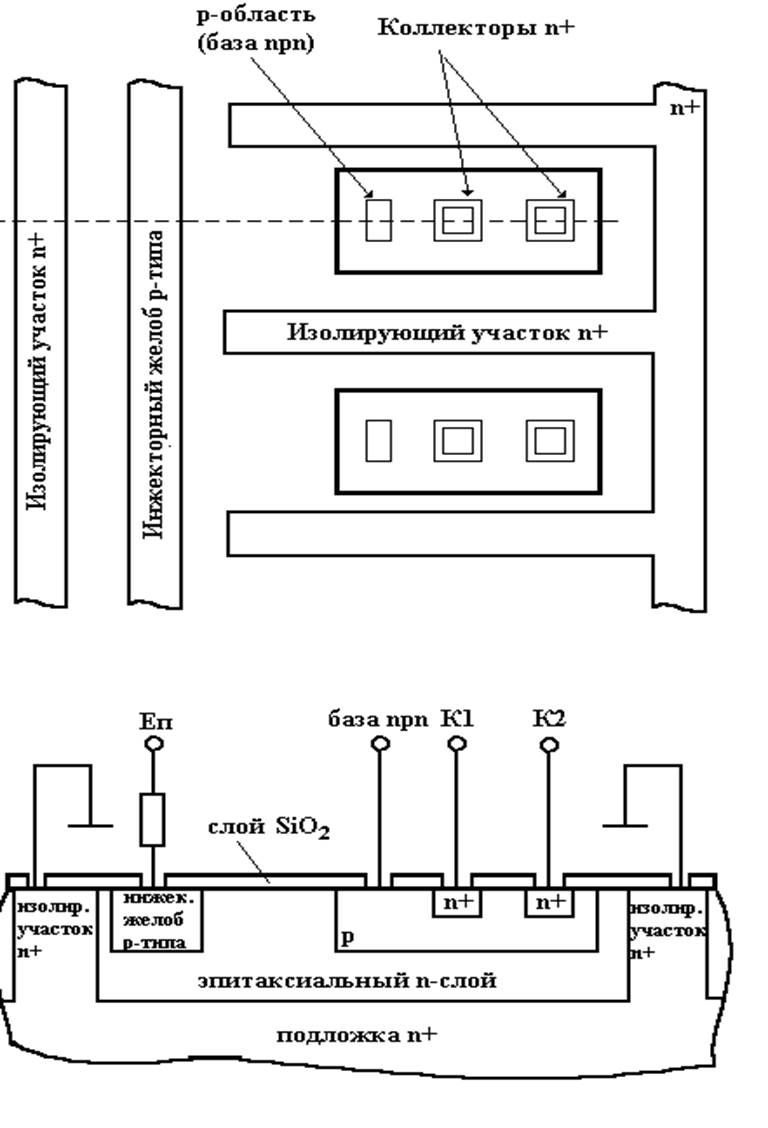

Для построения интегральных микросхем с высокой степенью интеграции и низкой потребляемой мощностью применяется интегральная инжекционная логика (И2Л), основным элементом которой является многоколлекторный транзистор. Базовый элемент И2Л содержит вертикальный n-p-n многоколлекторный транзистор и горизонтальный p-n-p транзистор. Структура и эквивалентная схема полупроводникового И2Л прибора представлены на рис. 12 и 13. В структуре совмещены область коллектора горизонтального p-n-p транзистора с областью базы вертикального n-p-n многоколлекторного транзистора. Поскольку p-n-p и n-p-n транзисторы совмещены, то для выполнения функций нагрузки и источников тока резисторы не требуются.

Заземлённые участки проводимости n+ используются для изоляции транзисторных n-p-n структур. Один инжекторный желоб р-типа, который служит эмиттером горизонтальных p-n-p транзисторов, используется для инжектирования тока в группу "островков" р-типа, являющихся коллекторами p-n-p и базами n-p-n транзисторов. Эпитаксиальный слой n-типа служит заземлённой базой горизонтальных p-n-p транзисторов и заземлёнными эмиттерами вертикальных n-p-n транзисторов. Так как в качестве коллекторов используется n+ область, напряжение пробоя коллектор-база мало, а ёмкость этого перехода относительно велика. Поперечный дырочный ток, который инжектируется в область базы n-p-n транзисторов, обеспечивает переход последних от закрытого состояния к открытому. Отсюда название - интегральная инжекционная логика.

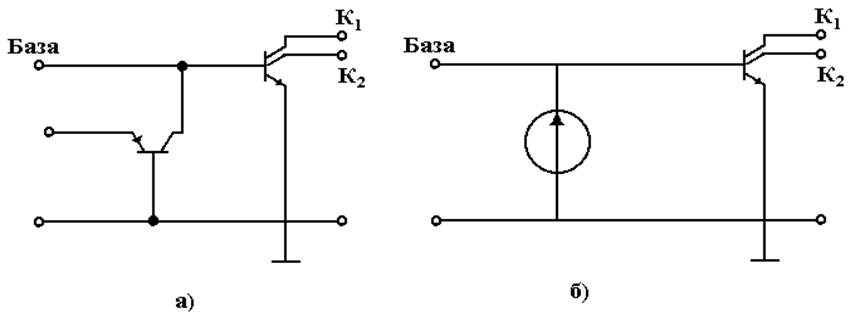

Горизонтальный p-n-p транзистор включён между базой и заземлённым эмиттером вертикального n-p-n многоколлекторного транзистора. Если сопротивление горизонтального p-n-p транзистора велико, то n-p-n транзистор попадает в режим насыщения и напряжение на коллекторах будет иметь низкий уровень (логический ноль). Если горизонтальный p-n-p транзистор открыт, то он шунтирует вход n-p-n вертикального транзистора (на его базе низкий уровень напряжения), n-p-n транзистор закроется и на выходе будет высокий уровень сигнала (логическая единица).

Сигналы высокого уровня (логическая единица) и низкого (логический ноль) в элементах И2Л имеют физический смысл в отличие от элементов ТТЛ, это действительно высокое и низкое напряжение. В схемах И2Л напряжение питания подаётся на инжекторный жёлоб, который является эмиттером всех горизонтальных p-n-p транзисторов структуры. На вход и выход вертикальных многоколлекторных n-p-n транзисторов напряжение питания не подаётся, к ним присоединяются аналогичные каскады логики. Вход (база вертикального многоколлекторного n-p-n транзистора) может быть соединен с несколькими коллекторами предыдущего каскада, а выходы (коллекторы) подсоединяются к базе следующего каскада.

Логическая единица на входе проявляется, когда входная цепь не шунтирует базу вертикального многоколлекторного n-p-n транзистора, а логический ноль – в случае шунтирования базы.

Логическая единица на выходе проявляется, когда коллекторы многоколлекторного n-p-n транзистора не шунтируют вход последующего каскада. При логическом нуле коллекторы открытого по p-n переходу Б-Э вертикального многоколлекторного n-p-n транзистора шунтируют «вход базы» следующей элементарной ячейки И2Л.

|

|

|

|

|

|

|

Рис.12. Структура базового И2Л вентиля: а - вид сверху; б - поперечное сечение

|

Рис.13. Эквивалентная схема структуры И2Л: а – с горизонтальным p-n-p транзистором; б – p-n-p транзистор заменён источником постоянного тока

|

|

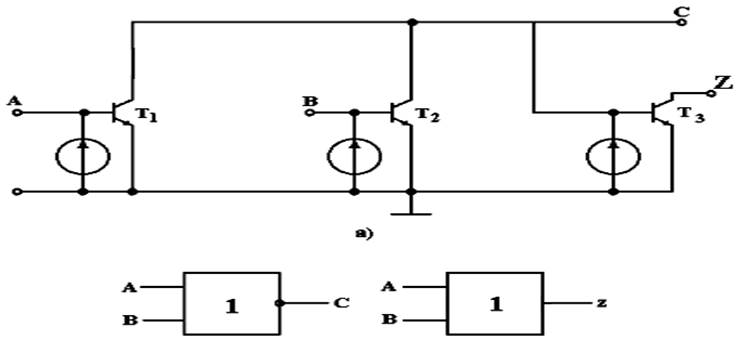

А |

В |

С |

Z |

|

0 |

0 |

1 |

0 |

|

0 |

1 |

0 |

1 |

|

1 |

0 |

0 |

1 |

|

1 |

1 |

0 |

1 |

б

Рис.14. Логический вентиль на элементах И2Л:

а – принципиальная схема; б – таблица истинности и условные логические обозначения

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.