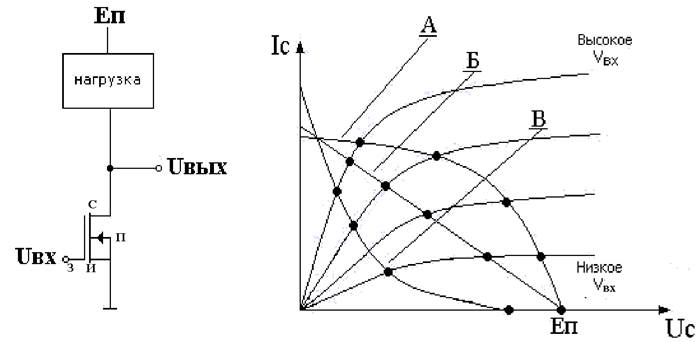

Для заряда ёмкости затвор-канал нужен минимальный ток затвора, что даёт возможность получать высокий коэффициент разветвления по выходу. Высокое входное сопротивление и небольшая ёмкость затвора МОП - транзистора делают выгодным его использование в качестве элемента памяти. Прибор с индуцированным каналом можно поддерживать в проводящем состоянии за счет заряда на конденсаторе, образованном затвором и каналом транзистора. У МОП - транзистора можно поменять местами сток с истоком, что исключительно удобно для построения некоторых типов переключающих схем. В качестве элемента возбуждения МОП-инвертора обычно используется n-канальный МОП-транзистор, нагрузкой могут быть: резистор (пассивная линейная нагрузка); n-канальный МОП-транзистор с индуцированным или встроенным каналом (пассивная нелинейная нагрузка); p-канальный МОП-транзистор с индуцированным каналом (активная нелинейная нагрузка). В современных МОП БИС резистивные нагрузочные элементы почти не применяются за исключением некоторых типов запоминающих устройств, в которых используется высокоомная нагрузка. Наибольшее распространение получили схемы с активной нагрузкой в виде р-канального МОП-транзистора с индуцированным каналом (КМОП-схемы). В КМОП-схемах цепи нагрузки и цепи возбуждения являются взаимно дополняющими, откуда и происходит название комплементарные.

Рис. 8. Характеристики n-МОП-транзистора (возбуждающий элемент) и нагрузочных элементов:

А – нагрузка - полевой транзистор со встроенным каналом; Б – нагрузка - резистор; В – нагрузка - полевой транзистор с индуцированным каналом

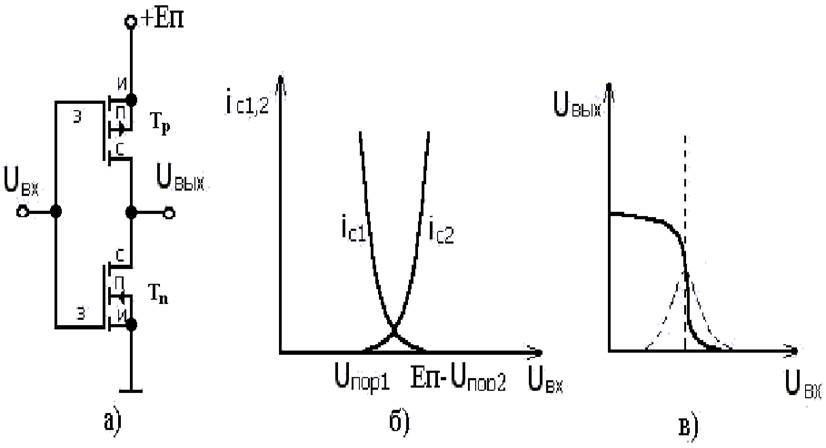

Схема КМОП-инвертора содержит два транзистора Тn и Тр с каналами n- и р-типа, соответственно. При положительном напряжении на входе транзистор Тn открыт, а транзистор Тр закрыт. На выходе получаем низкий уровень напряжения, приблизительно равный нулю. Если на входе ноль, то транзистор Тn закрыт, а транзистор Тр открыт. На выходе получаем высокий уровень напряжения, приблизительно равный напряжению источника питания. В обоих состояниях ток, потребляемый от источника питания, практически равен нулю. Обычно в БИС и СБИС выход инвертора соединен с входами аналогичных инверторов-нагрузок. В этом случае мощность, потребляемая в статическом режиме, практически равна нулю, что является важнейшим преимуществом КМОП -микросхем по сравнению с любыми другими микросхемами.

В КМОП-инверторе транзисторы работают в противофазе, что улучшает быстродействие. Подложки каждого из транзисторов соединены с их истоками, что предотвращает открывание p-n – пе-реходов. На рис. 9 приведены сквозные передаточные характеристики транзисторов с учетом их включения и передаточная характеристика инвертора.

Рис. 9. Схема КМОП-инвертора; а – схема инвертора; б – входные характеристики транзисторов; в – передаточная характеристика КМОП-инвертора

Оптимальная форма передаточной характеристики достигается при одинаковых параметрах транзисторов: у них должна быть одинаковой крутизна входных характеристик Sn = Sp (S = dIc / dUзи при Uси = const). Пороговое напряжение n-канального возбуждающего МОП с индуцированным каналом должно быть приблизительно равно (по модулю) напряжению отсечки р-канального нагрузочного МОП.

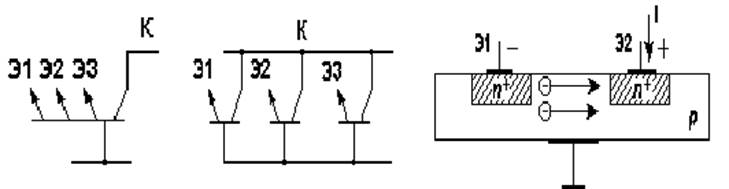

Многоэмиттерный транзистор (МЭТ) является типичным порождением микроэлектроники. Такие транзисторы составляют основу весьма распространённого класса цифровых ИС – схем транзисторно-транзисторной логики (ТТЛ). Количество эмиттеров в МЭТ может составлять от двух до восьми. В первом приближении МЭТ можно рассматривать как совокупность отдельных транзисторов с соединёнными базами и коллекторами (рис.10).

Особенности МЭТ как единой структуры следующие.

Во-первых, каждая пара смежных эмиттеров вместе с разделяющим их p-слоем базы образует горизонтальныйтранзистор типа n+-p-n+. Если на одном из эмиттеров действует прямое напряжение, а на другом обратное, то первый будет инжектировать электроны, а второй будет собирать. Собирать второй эмиттер будет те электроны, которые были инжектированы через боковую поверхность эмиттера и прошли без рекомбинации расстояние между эмиттерами. Такой горизонтальный транзисторный эффект является для МЭТ паразитным: в обратносмещённом переходе, который должен быть запертым, будет протекать ток. Чтобы избежать этого горизонтального транзисторного эффекта, расстояние между эмиттерами должно превышать диффузионную длину носителей в базовом слое.

а б

Рис. 10. Многоэмиттерный транзистор: а – схемные модели; б – взаимодействие между смежными эмиттерами

Во-вторых, важно, чтобы МЭТ имел как можно меньший инверсный коэффициент передачи тока. В противном случае в инверсном режиме (когда эмиттеры находятся под обратным напряжением, а коллектор под прямым) носители, инжектируемые коллектором, будут в значительной мере достигать эмиттеров. Чтобы уменьшить инверсный коэффициент передачи в МЭТ, искусственно увеличивают сопротивление пассивной области базы. Для этого удаляют омический базовый контакт от активной области транзистора (рис.11,б). При такой топологии транзистора сопротивление пассивной области базы может составлять 200-300 Ом. Поэтому прямое напряжение на коллекторном переходе (в инверсном режиме включения) будет меньше, чем вблизи базового контакта, приблизительно на 0.15-0.2 вольта и инжекция электронов из коллектора в активную область базы будет незначительной, а паразитные токи через эмиттеры будут малы.

Схема простейшего элемента ТТЛ приведена на рис.11,а. Она содержит входной двухэмиттерный транзистор T1, в базовой цепи которого включён резистор R1, и выходной инвертор на транзисторе T2, в коллекторной цепи которого включён резистор R2. Многоэмиттерный транзистор выполняет логическую операцию "И" над входными логическими переменными А и В, а на выходе элемента реализуется функция "И-НЕ".

Рассмотрим принцип действия логического элемента (ЛЭ) в статическом режиме.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.