8

несимметричных каналов

7 дифференциальных каналов

2 дифференциальных канала с выборочным усилением из 1x, 10x и 200x

–

Двухпроводной последовательный интерфейс, ориентированный не передачу данных в

байтном формате

– Два канала программируемых последовательных УСАПП

– Последовательный интерфейс SPI с поддержкой режимов

ведущий/подчиненный

– Программируемый сторожевой таймер со встроенным

генератором

– Встроенный аналоговый компаратор

–

53 –программируемые линии ввода-вывода

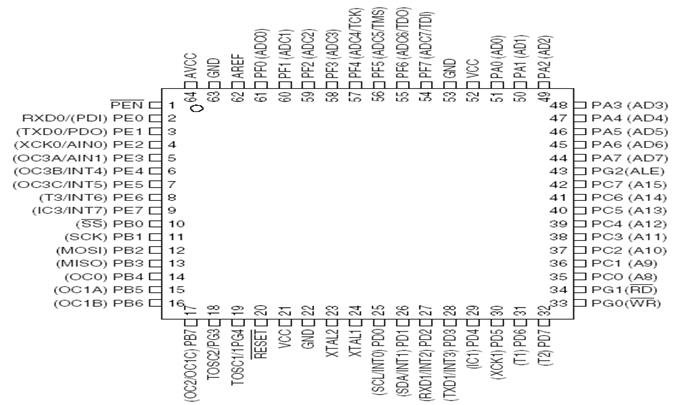

– 64-выв. корпус TQFP

Рисунок 3.2 Цоколевка ATmega128

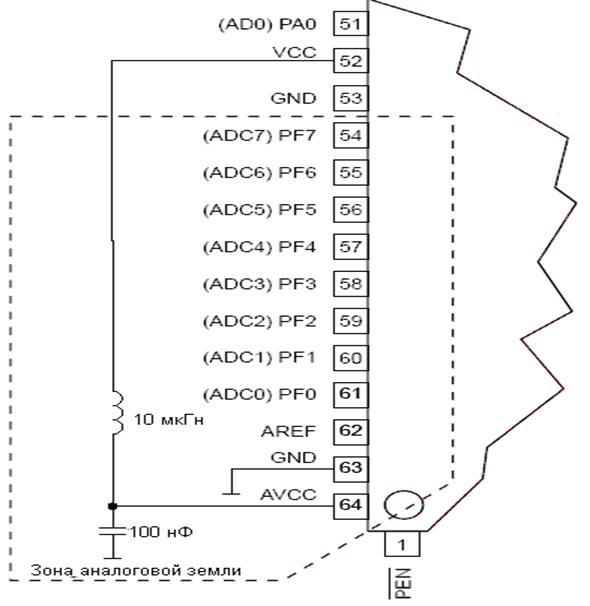

Типовая схема включения ATmega128 изображена на Рис. 3.3 и 3.4

Рисунок 3.3 Типовая схема включения ATmega128

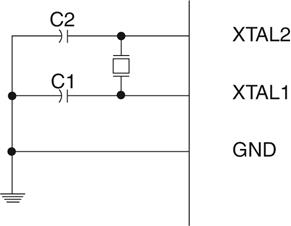

Рисунок 3.4 Типовая схема подключения кварцевого резонатора

Тогда согласно Рис. 3.3 и схеме электрической принципиальной (Приложение Б) С8=100нФ , С9=0,1 мкФ. Тип и основные характеристики конденсаторов приведены в приложении В.

3.3. Преобразователь уровней

В качестве преобразователя уровней возьмем микросхему MAX202.

Основные характеристики:

|

Количество приемо/передатчиков: |

2Dr/2Re |

|

Скорость передачи: |

120 кБод |

|

Напряжение питания, В: |

5 |

|

Электростатическая защита: |

да |

|

Температурный диапазон: |

0 +70 |

|

Налич. внеш. конденсаторов: |

- |

|

Корпус: |

SO16 |

Типовая схема включения приведена на рис 3.5

Рисунок 3.5 Типовая схема включения MAX202

Тогда согласно Рис. 3.3 и схеме электрической принципиальной (Приложение А) C4= C5= C6= 100 нФ,C7=100нФ. Тип и основные характеристики конденсаторов приведены в приложении Б.

3.4. Внешняя память

Особенности

• Быстро Прочитанное Время доступа – 70 нс

• Операция Программы Сектора

– Единственная Перепрограмма Цикла (Стирают и Программируют)

– 512 Секторов (128 байтов/сектора)

– Внутренние коды Адреса и Данных для 128 байтов

• Внутренний Контроль за Программой и Таймер

• Аппаратные средства и Защита Данных Программного обеспечения

• Быстрое Время цикла Программы Сектора – 10 миллисекунд

• ДАННЫЕ, Голосующие для Конца Обнаружения Программы

• Низкое мощность

– 50 мА Активный Поток

– 300 μA CMOS Резервный Поток

• Типичная Выносливость> 10 000 Циклов

• Единственный 5V ± 10%-ая Поставка

• CMOS и Совместимые Входы и выходы TTL

Описание

AT29C512 5.t только Вспышка в системе, программируется и стираеься прочитывается память (PEROM). Его 512 КБ памяти организованы как 65 536 слов на 8 битов. Произведенный с передовой энергонезависимой технологией Atmel’s CMOS, предложениями устройства времена доступа к 70 не уточнено с разложением власти только 275 мВт по индустриальной температуре диапазон. Когда устройство отсеяно, резервный поток CMOS меньше

чем 300 μA. Выносливость устройства такова, что любой сектор может типично писаться сверх 10 000 раз.

Чтобы учесть простой reprogrammability в системе, AT29C512 не требует высоко входные напряжения для того, чтобы программировать устройство. Чтение данных из устройства подобно чтению от стираемой программируемой постоянной памяти.

Перепрограммирование AT29C512 выполнено на основе сектора; 128 байтов данных загруженный в устройство и затем одновременно запро-граммированный.Во время цикла перепрограммы местоположения адреса и 128 байтов данных внутреннезапиравший, освобождая автобус адреса и данных для других операций. После инициирования из цикла программы устройство автоматически сотрет сектор и затем программу запиравшие данные, используя внутренний таймер контроля. Конец цикла программы может быть обнаруженный опросом ДАННЫХ I/O7. Как только конец цикла программы был обнаруженный, новый доступ для прочитанного или программы может начаться.

Рисунок 3.6.Типовая схема включения Flesh памяти

4. Алгоритм процесса управления формированием кода данных

для накопителя информации

Алгоритм разработан на основании анализа принципа работы устройства формирования кода данных для накопителя информации и представлен на рисунку 2.3.

При разработке алгоритма ввели использованы следующие обозначения:

FT-сигнал тактовой частоты;

Ry-сигнал установки формирователя адреса в исходное состояние;

NFT-порядковый номер импульса сигнала тактовой частоты;

ОШ1-сигнал ошибки результата сравнение свертки по модулю 2 и содержимого 32-горазряда кода последовательного;

ОШ2-сигнал ошибки по результата анализа содержимого матрицы состояния кода последовательного;

УС-сигнал на устройство сопряжения о наличии ошибки в сообщении;

ЗАП-сигнал разрешения записи;

ЧТ-сигнал разрешения чтения;

КПО-код последовательный;

R-сигнал установки устройства;управление в исходное состояие.

Рис.4.1.Алгоритм процесса управления формированием кода данных для накопителя информации.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.