Розряд 0 – UCPOL0. Полярність синхронізації. Використовується тільки в синхронному режимі. Якщо використовується асинхронний режим, то в даний біт необхідно записати логічний 0. У синхронному режимі біт UCPOL0 визначає співвідношення між вибіркою вхідних даних і відновленням переданих даних і сигналом тактування синхронного зв'язку (таблиця 64).

Таблиця 64 - Результат дії біта UCPOL0

|

UCPOL0 |

Відновлення переданих даних (вивід на лінію Tx) |

Вибірка прийнятих даних (уведення на лінію Rx) |

|

0 |

По фронту ХСК |

По спаду ХСК |

|

1 |

По спаду ХСК |

По фронту ХСК |

Регістр генератора швидкості зв'язку (UBRR) і пов'язаний з ним віднімаючий лічильник функціонують як програмувальний переддільник або генератор швидкості зв'язку. Віднімаючий лічильник тактується системною синхронізацією (fosc) і перезавантажується значенням з регістра UBRR щоразу під час досягнення нульового значення або після записування регістра UBRRL. Тактовий сигнал генерується щоразу під час досягнення лічильником нульового значення. Даний тактовий сигнал є тактовим виходом генератора швидкості зв'язку. Передавач ділить частоту генератора швидкості зв'язку на 2, 8 або 16 залежно від режиму роботи. Модулі виявлення синхронізації й даних приймача підключені безпосередньо до тактового виходу генератора швидкості зв'язку. Однак, цифрові автомати модулів виявлення використають 2, 8 або 16 станів залежно від режиму, що задають біти UMSEL, U2X і DDR_XCK.

Структура регістра швидкості зв'язку представлена в таблиці 65.

Таблиця 65 - Регістр швидкості зв'язку UBRR0L й UBRR0H

|

Розряд |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

UBRR0H [11:8] |

||||||||

|

UBRR0L [7:0] |

||||||||

|

Зчитування/ записування |

Зп. /Зч. |

Зп. / Зч. |

Зп. / Зч. |

Зп. / Зч. |

Зп. / Зч. |

Зп. / Зч. |

Зп. / Зч. |

Зп. / Зч. |

|

Вих. значення |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

0 |

Розряди 15-12 - зарезервовані розряди. Ці розряди зарезервовані для майбутнього використання.

Розряди 11-0 - задають значення швидкості зв'язку УСАПП. Регістр UBRR0H містить 4 старших розряди, а UBRR0L 8 молодших розрядів значення швидкості УСАПП0. Якщо під час передачі або прийому змінити швидкість зв'язку, то сеанс зв'язку буде порушений. Записування до регістру UBRR0L ініціює відновлення переддільника швидкості зв'язку.

Перед початком сеансу зв'язку необхідно виконати ініціалізацію УСАПП. Процес ініціалізації звичайно складається з установки швидкості зв'язку, задання формату посилки й дозволу роботи передавача й приймача. Якщо використовується керування зв'язком згідно переривань, то під час ініціалізації необхідно, щоб був скинутий прапорець загального дозволу переривань (тобто необхідно заборонити всі переривання).

Робота передавача УСАПП дозволяється шляхом установлення біта дозволу передачі (TXEN) у регістрі UCSRB. Після дозволу, функція виводу Tx як звичайного порту заміняється на функцію виходу послідовної передачі даних. Швидкість зв'язку, режим роботи й формат посилки повинні бути встановлені одноразово перед початком будь-якої передачі. Якщо використовується синхронна робота, то функція виводу XCK також заміняється на альтернативну - синхронізація передачі.

Робота приймача УСАПП дозволяється, якщо записати логічну 1 до біта дозволу роботи приймача (RXEN) у регістрі UCSRB. Після дозволу роботи приймача звичайне призначення виводу Rx замінюється на альтернативне: вхід послідовного уведення даних приймача УСАПП. Швидкість зв'язку, режим роботи й формат посилки повинні бути встановлені одноразово перед початком виконання прийому даних. Якщо використовується синхронна робота, то вивід XCK буде використовуватися для синхронізації зв'язку.

Приклад конфігурації універсального синхронно-асинхронного приймача-передавача (УСАПП) мікроконтролера ATmega128

Настроїти послідовну передачу п'яти байт даних за допомогою УСАПП0, в асинхронному режимі, кількість біт 8, швидкість передачі без подвоєння, без паритету з 2-ма стоповими бітами. Масив даних: 0x20,0x34,0x40,0x45,0x98.

1. Запишемо стан регістра А керування й статусу (таблиця 66). Регістр UCSR0A буде мати наступний варіант установок: всі біти приймуть значення логічного 0, крім прапорця завершення передачі.

Таблиця 66 – Варіант установок регістра А керування й статусу UCSR0A

|

RXC0 |

TXC0 |

UDRE0 |

FE0 |

DOR0 |

UPE0 |

U2X0 |

MPCM0 |

|

0 |

1 |

0 |

0 |

0 |

0 |

0 |

0 |

2. Запишемо стан регістра В керування й статусу (таблиця 67). Регістр UCSR0B буде містити наступні настроювання: дозвіл переривання після завершення передачі та дозвіл роботи передавача необхідно встановити в стан логічної 1.

Таблиця 67 – Варіант установок регістра В керування й статусу UCSR0В

|

RXCIE0 |

TXCIE0 |

UDRIE0 |

RXEN0 |

TXEN0 |

UCSZ02 |

RXB80 |

TXB80 |

|

0 |

1 |

0 |

0 |

1 |

0 |

0 |

0 |

3. Запишемо стан регістра С керування й статусу (таблиця 68). Регістр UCSR0С буде містити наступні настроювання: число стоп-біт 2, формат переданих даних 8 біт.

Таблиця 68 – Варіант установок регістра С керування й статусу UCSR0С

|

- |

UMSEL0 |

UPM01 |

UPM00 |

USBS0 |

UCSZ01 |

UCSZ00 |

UCPOL0 |

|

- |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

Програма

void InitPort(void);

void InitADC(void);

void InitUSART(void);

const int SKOR=0x237;

int resh,resl,i;

void InitPort(void)

{DDRF&=~(1<<DDF0);

DDRE|=(1<<DDE1);

}

void InitADC(void)

{ADMUX=0x40;

ADCSRA=0xec;

}

void InitUSART (void)

{UBRR0H=(SKOR>>8);

UBRR0L=SKOR;

UCSR0A=0x00;

UCSR0B=0x48;

UCSR0C=0x3e;

UDR0=0x00;

}

SIGNAL(SIG_ADC)

{ resh=ADCH;

resl=ADCL;

}

SIGNAL(SIG_USART0_TRANS)

{cli();

switch (i)

{case 0:

UDR0=resh;

i=1;

break;

case 1:

UDR0=resl;

i=0;

break;

}

sei();

}

void main(void)

{InitPort();

InitADC();

InitUSART();

sei();

while(1) {}

}

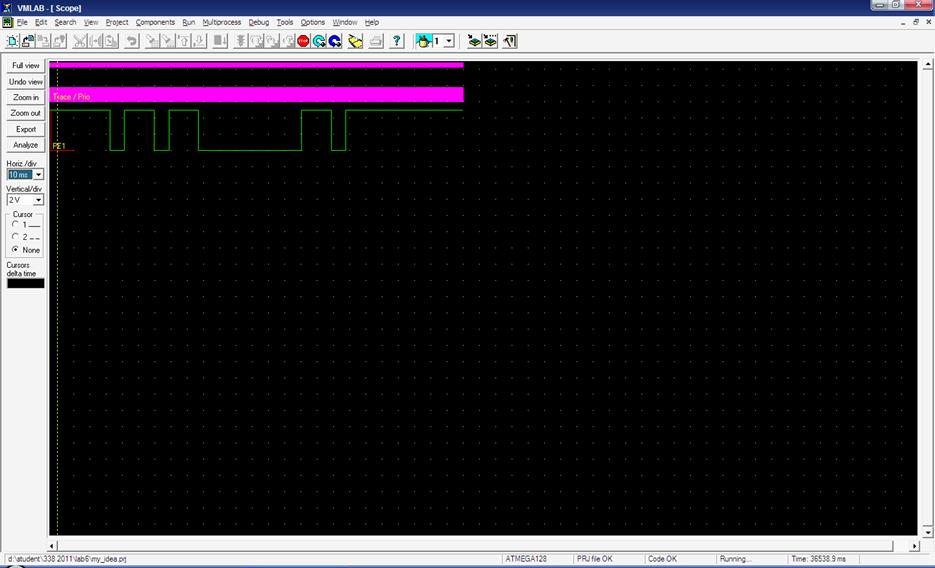

V1 PF0 VSS SLIDER_1(0 5) ;x: Panel sliders 1 - 3

. PLOT V(PE1)

Висновок: на цій лабораторній роботі я дослідила принцип побудови, освоїла методику конфігурації й особливості застосування синхронно-асинхронного послідовного приймача-передавача мікроконтролера ATmega128

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.