Лабораторна робота № 5

Дослідження і конфігурація послідовного периферійного інтерфейсу - SPI мікроконтролера ATmega128

Мета роботи: дослідити принцип побудови, освоїти методику конфігурації й особливості застосування послідовного периферійного інтерфейсу - SPI мікроконтролера ATmega128

Завдання до лабораторної роботи

2 варіант

У режимі без подвоєння швидкості передати у ведучому режимі масив з п'яти констант. Передній

фронт – установка даних наростаючим фронтом. Задній фронт – вибірка даних спадаючим фронтом.

Теоретичні основи

Інтерфейс SPI дозволяє організувати послідовну синхронну високошвидкісну передачу даних між ATmega128 й іншим периферійним пристроєм або між декількома AVR-мікроконтролерами.

Основні відмінні риси:

- повнодуплексна, трьохпровідна синхронна передача

даних;

- ведуча або підпорядкована робота;

- передача першим молодшого або старшого біта;

- сім програмованих швидкостей зв'язку;

- прапорець переривання для індикації закінчення

передачі даних;

- захисний прапорець під час повторного

записування;

- пробудження з режиму холостого ходу (Idle);

- режим ведучого (майстра) SPI з подвоєнням

швидкості (CK/2).

Система складається із двох зсувних регістрів і генератора провідної синхронізації. Ведучий SPI ініціює сеанс зв'язку подачею низького рівня на вхід SS того підпорядкованого пристрою, з яким необхідно обмінюватися даними. Обоє респонденти (ведучий і підпорядкований) готують дані до передачі у своєму зсувному регістрі, при цьому на стороні ведучого генеруються також імпульси синхронізації на лінії SCK. По лінії MOSI завжди здійснюється передача даних від ведучого до підпорядкованого, а по MISO, навпаки, від підпорядкованого до майстра. Після закінчення передачі кожного пакета даних ведучий SPI повинен засинхронізувати підпорядкований шляхом подачі високого рівня на лінію SS (вибір підпорядкованого інтерфейсу).

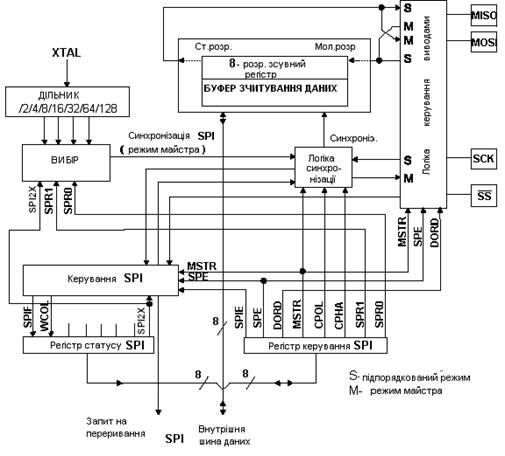

Функціональна схема інтерфейсу SPI представлена на рисунку16.

Рисунок 16 - Функціональна схема інтерфейсу SPI

Якщо робота SPI дозволена, то дозволяється альтернативний напрямок виводів MOSI, MISO, SCK і SS згідно таблиці 46.

Таблиця 46 - Напрямок виводів SPI

|

Вивід |

Напрямок для ведучго SPI |

Напрямок для підпорядкованого SPI |

|

MOSI |

Визначається користувачем |

Вхід |

|

MISO |

Вхід |

Визначається користувачем |

|

SCK |

Визначається користувачем |

Вхід |

|

SS |

Визначається користувачем |

Вхід |

Підпорядкований режим

Після переводу SPI у режим підпорядкованого вивід SS завжди працює як вхід. У цьому випадку SPI активізується, якщо на вхід SS подати низький рівень, а вивід MISO стає виходом, якщо так установить користувач. Всі інші виводи працюють як входи. Якщо на вхід SS подати високий рівень, то всі виводи стануть входами й SPI перейде в пасивний стан, у якому блокується прийом вхідних даних. Логіка SPI скидається як тільки на вивід SS подається високий рівень.

Вивід SS зручно використовувати для пакетної/байтной синхронізації, що дозволяє підтримати синхронність роботи підпорядкованого лічильника біт і ведучого генератора синхронізації. Якщо на вивід SS подати високий рівень, то підпорядкований SPI скине передавальну й приймальну логіку й втратить будь-які не повністю прийняті дані в зсувному регістрі.

Провідний режим

Якщо SPI настроєний як майстер (установлений біт MSTR в регістрі SPCR), то користувач може задати бажаний напрямок виводу SS.

Якщо SS настроєний на вивід, то він працює як звичайна лінія цифрового виводу й не впливає на систему SPI. Звичайно він використовується для керування виводом SS підлеглого SPI.

Якщо SS настроїти як вхід, то на ньому має бути присутнім високий рівень, щоб гарантувати роботу ведучого SPI. Якщо SPI настроєний як майстер, у якого вив. SS настроєний як вхід, то подача на цей вхід низького рівня зовнішньою схемою буде інтерпретована як переведення у підлеглий режим після запиту іншого ведучого SPI, після чого почнеться передача даних.

У таблиці 47 представлене призначення бітів регістра керування SPI - SPCR.

Таблиця 47 - Призначення бітів регістра керування SPI – SPCR

|

№ біта |

Ім'я |

Призначення |

|

7 |

SPIE |

Дозвіл переривання SPI |

|

6 |

SPE |

Дозвіл SPI |

|

5 |

DORD |

Порядок зсування даних |

|

4 |

MSTR |

Вибір ведучого/підпорядкованого |

|

3 |

CPOL |

Полярність синхронізації |

|

2 |

CPHA |

Фаза синхронізації |

|

1 |

SPR1 |

Вибір частоти синхронізації SPI біт 1 |

|

0 |

SPR0 |

Вибір частоти синхронізації SPI біт 0 |

Розряд 7 - SPIE. Дозвіл переривання SPI. Якщо встановлено прапорець SPIF у регістрі SPSR і встановлений біт загального дозволу переривань I у регістрі SREG, то установлення даного біта призведе до виконання процедури обробки переривання після закінчення передачі SPI.

Розряд 6 - SPE. Дозвіл SPI. Якщо в SPE записати логічну 1, то дозволяється робота SPI. Даний біт повинен бути встановлений, якщо необхідно використати SPI незалежно від того, в якому режимі він буде працювати.

Розряд 5 - DORD. Порядок зсування даних. Якщо DORD=1, то під час передачі слова даних першим передається молодший розряд. Якщо ж DORD=0, то першим передається старший розряд.

Розряд 4 - MSTR. Вибір ведучого/підпорядкованого. Якщо в даний біт записана логічна 1, то SPI працює як ведучий, інакше (MSTR=0) як підпорядкований. Якщо SS настроєний як вхід і до нього прикладений низький рівень, коли MSTR дорівнював 1, то біт MSTR автоматично скидається й установлюється прапорець переривання SPIF у регістрі SPSR. Для поновлення ведучого режиму SPI користувач повинен передбачити програмне установлення біта MSTR.

Розряд 3 - CPOL. Полярність синхронізації. Якщо даний біт дорівнює логічній 1, то SCK має високий рівень у стані очікування. Якщо CPOL=0, то SCK має низький рівень у стані очікування. У таблиці 48 узагальнене функціонування бітів CPOL.

Таблиця 48 - Результат дії біта CPOL

|

CPOL |

Передній фронт |

Задній фронт |

|

0 |

Наростаючий |

Спадаючий |

|

1 |

Спадаючий |

Наростаючий |

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.