Розряд 2 - CPHA. Фаза синхронізації. Значення біта фази синхронізації (CPHA) визначає по якому фронту SCK відбувається вибірка даних. У таблиці 49 узагальнена дія біта CPHA.

Таблиця 49 - Результат дії біта CPHA

|

CPHA |

Передній фронт |

Задній фронт |

|

0 |

Вибірка |

Установлення |

|

1 |

Установлення |

Вибірка |

Комбінація бітів CPHA й CPOL задає чотири можливих режими послідовної передачі даних.

Біти даних виводяться зсуванням і фіксуються на вході протилежними фронтами синхросигналу SCK, тим самим гарантуючи достатній час на встановлення сигналів даних.

Розряди 1, 0 - SPR1, SPR0. Біти вибору частоти синхронізації SPI. Дані біти задають частоту синхронізації на виводі SCK у режимі майстра. SPR1 і SPR0 ніяк не впливають в режимі підпорядкованого. Зв'язок між змістом бітів SPR1, SPR0 і частотою SCK представлений у таблиці 50.

Таблиця 50 - Зв'язок між умістом бітівSPR1, SPR0 і частотою SCK

|

SPI2X |

SPR1 |

SPR0 |

Частота SCK |

|

0 |

0 |

0 |

fosc /4 |

|

0 |

0 |

1 |

fosc /16 |

|

0 |

1 |

0 |

fosc /64 |

|

0 |

1 |

1 |

fosc /128 |

|

1 |

0 |

0 |

fosc /2 |

|

1 |

0 |

1 |

fosc /8 |

|

1 |

1 |

0 |

fosc /32 |

|

1 |

1 |

1 |

fosc /64 |

Призначення бітів регістра статусу SPSR представлені в таблиці 51.

Таблиця 51 - Призначення бітів регістра статусу SPSR

|

№ біта |

Ім'я |

Призначення |

|

7 |

SPIF |

Прапорець переривання по SPI |

|

6 |

WCOL |

Прапорець повторного записування |

|

5 – 1 |

– |

Зарезервовані біти |

|

0 |

SPI2X |

Вибір частоти синхронізації SPI біт 0 |

Розряд 7 - SPIF. Прапорець переривання по SPI. Прапорець SPIF установлюється після завершення послідовної передачі. Переривання генерується в тому випадку, якщо встановлено біт SPIE у регістрі SPCR і дозволені загальні переривання. Якщо SS настроєний як вхід і до нього прикладений низький рівень, то, якщо SPI перебував у режимі майстра, також установиться прапорець SPIF.

Розряд 6 - WCOL. Прапорець повторного записування. Біт WCOL установлюється, якщо виконано записування до регістру даних SPI (SPDR) під час передачі даних.

Розряди 5..1 - Res. Зарезервовані біти.

Розряд 0 - SPI2X. Біт подвоєння швидкості SPI. Якщо в даний біт записати лог. 1, то швидкість роботи SPI (частота SCK) подвоїться, якщо SPI перебуває в режимі майстра.

Регістр даних SPI має доступ на зчитування і записування і призначений для обміну даними між файлом регістрів (r0...r31) і зсувним регістром SPI. Записування до даного регістру ініціює передачу даних. Під час зчитування даного регістра фактично зчитується вміст приймального буфера зсувного регістра. Структура регістра даних SPI - SPDR наведена в таблиці 52.

Таблиця 52 - Регістр даних SPI – SPDR

|

Розряд |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

|

|

Ст. розряд |

Мол. розряд |

SPDR |

|||||||

|

Зчитування/ записування |

Зч. / Зп |

Зч. / Зп |

Зч. / Зп |

Зч. / Зп |

Зч. / Зп |

Зч./ Зп |

Зч./ Зп |

Зч. / Зп |

|

|

Вих. значення |

x |

x |

x |

x |

x |

x |

x |

x |

Приклад конфігурації послідовного периферійного інтерфейсу - SPI мікроконтролера ATmega128

Настроїти послідовний периферійний інтерфейс на передачу п'яти байт даних у режимі майстер.

1. Запишемо стан регістра керування SPCR за заданої умови.

Регістр керування SPCR буде мати наступний варіант установок згідно таблиці 53: дозвіл переривання SPI, запуск, порядок зсування даних убік молодших розрядів, режим ведучого, SCK має низький рівень у стані очікування, вибірка даних по задньому фронту.

Таблиця 53 - Варіант установок регістра керування SPI – SPCR

|

SPIE |

SPE |

DORD |

MSTR |

CPOL |

CPOL |

SPR1 |

SPR0 |

|

1 |

1 |

1 |

1 |

0 |

0 |

1 |

0 |

2. Запишемо стан регістра статусу SPSR.

У регістрі статусу встановимо біт подвоєння швидкості передачі в стан логічного 0, що значитиме нормальну швидкість передачі згідно таблиці 54.

Таблиця 54 - Регістр статусу SPSR

|

SPIF |

WCOL |

SPI2X |

|

– |

– |

0 |

Програма

void InitPorts(void);

void InitADC(void);

void InitSPI(void);

int adch, adcl,i;

void InitPorts(void)

{ DDRF=0x00;

DDRB=0x07;

}

void InitADC(void)

{ADMUX=0x40;

ADCSRA=0xfd;

}

void InitSPI(void)

{SPCR=0xdb;

SPDR=adch;

}

SIGNAL(SIG_ADC)

{adch=ADCH;

adcl=ADCL;

}

SIGNAL(SIG_SPI)

{ cli();

switch (i)

{case 0:

SPDR=adch;

i=1;

break;

case 1:

SPDR=adcl;

i=0;

break;

}

sei();

}

void main (void)

{ InitPorts();

InitADC();

InitSPI();

sei();

while(1){}

}

V PF0 VSS SLIDER_1(0 5) ;x: Panel sliders 1 - 3

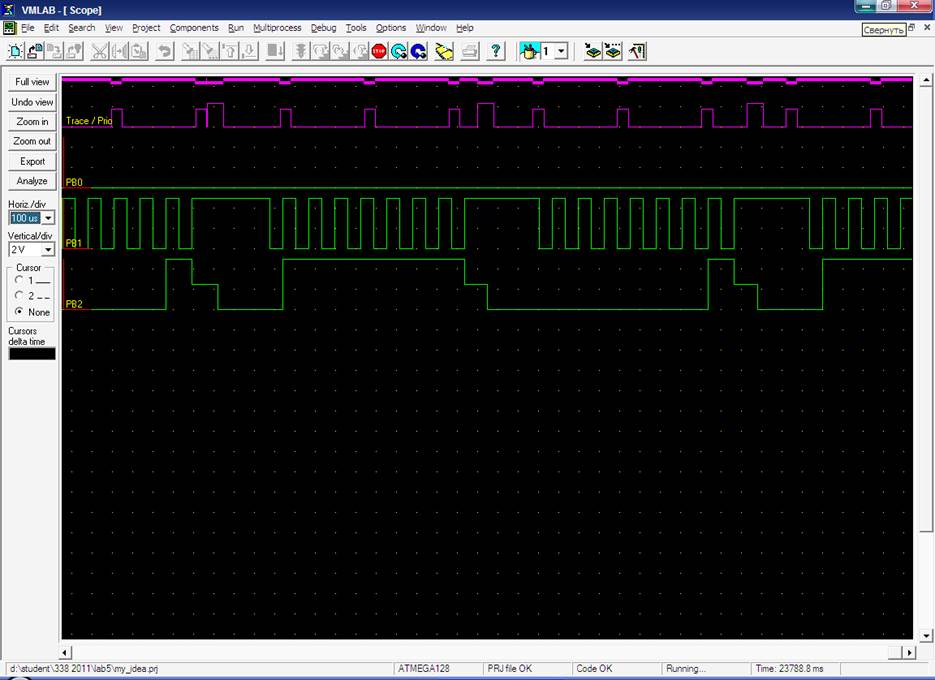

.PLOT V(PB0) V(PB1) V(PB2)

Висновок: на цій лабораторній роботі ядослідила принцип побудови, освоїла методику конфігурації й особливості застосування послідовного периферійного інтерфейсу - SPI мікроконтролера ATmega128

Лабораторна робота № 6

Дослідження і конфігурація керованого синхронно-асинхронного послідовного приймача-передавача мікроконтролера ATmega128

Мета роботи: дослідити принцип побудови, освоїти методику конфігурації й особливості застосування синхронно-асинхронного послідовного приймача-передавача мікроконтролера ATmega128

Завдання до лабораторної роботи

2 варіант

Передати масив із семи 6-розрядних слів. У структуру посилки включити перевірку паритету на непарність і два стоп-біти.

Теоретичні основи

Універсальний синхронно-асинхронний послідовний приймач-передавач (УСАПП, USART) призначений для організації гнучкого послідовного зв'язку між двома або декількома мікроконтролерами.

Відмінні риси:

- повнодуплексна робота (окремі регістри прийому й

передачі);

- асинхронна або синхронна робота;

- ведуче або підпорядковане тактування зв'язку в

синхронному режимі роботи;

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.