Лабораторна робота № 4

Тема роботи: ДОСЛІДЖЕННЯ Й КОНФІГУРУВАННЯ 10-РОЗРЯДНОГО АЦП ТА АНАЛОГОВОГО КОМПАРАТОРА МІКРОКОНТРОЛЕРА ATMEGA128

Мета роботи: дослідити принцип побудови 10-розрядного АЦП й аналогового компаратора мікроконтролера ATmega128, освоїти методику його конфігурування і особливості застосування.

Завдання до лабораторної роботи

|

Варіант |

Завдання |

|

1 |

Подати дві напруги, що змінюються в діапазоні 2...4 В, з резистивних дільників (SLIDER) S1, S2 на входи AIN1, AIN0 компаратора. Під час збігу напруг на компараторі запустити АЦП у стартостопному режимі й перетворити напругу, що подається на лінію 2 з дільника (SLIDER) S3 у діапазоні 1…3 В |

Теоретичні основи

Аналогово-цифровий перетворювач

АЦП мікроконтролера ATmega128 призначено для перетворення вхідної аналогової напруги в 10-розрядний код методом послідовних наближень.

Основні відмінні риси:

- 10-розрядна здатність;

- інтегральна нелінійність – 0,5 молодшого

розряду;

- абсолютна похибка – ±2 молодших розрядів;

- час перетворення – 65…260 мкс;

- частота перетворення – до 15 тис. у секунду

при максимальній здатності;

- вісім мультиплексованих однополярних входів;

- сім диференціальних вхідних каналів;

- два диференціальних вхідних канали

з опціональним посиленням на 10 і 200;

- подання результату з лівобічним або

правобічним вирівнюван-ням у 16-розрядному слові;

- діапазон вхідної напруги АЦП – 0...VCC;

- вибіркове внутрішнє джерело опорної напруги

(ДОН) на 2,56 В;

- режими одиночного перетворення і

автоматичного пере-запуску;

- переривання після завершення перетворення

АЦП;

- механізм заглушування шумів у режимі сну.

ATmega128 містить 10-розрядний АЦП послідовного наближення. АЦП пов'язаний з 8-канальним аналоговим мультиплексором, вісім однополярних входів якого з’єднано з лініями порту F.

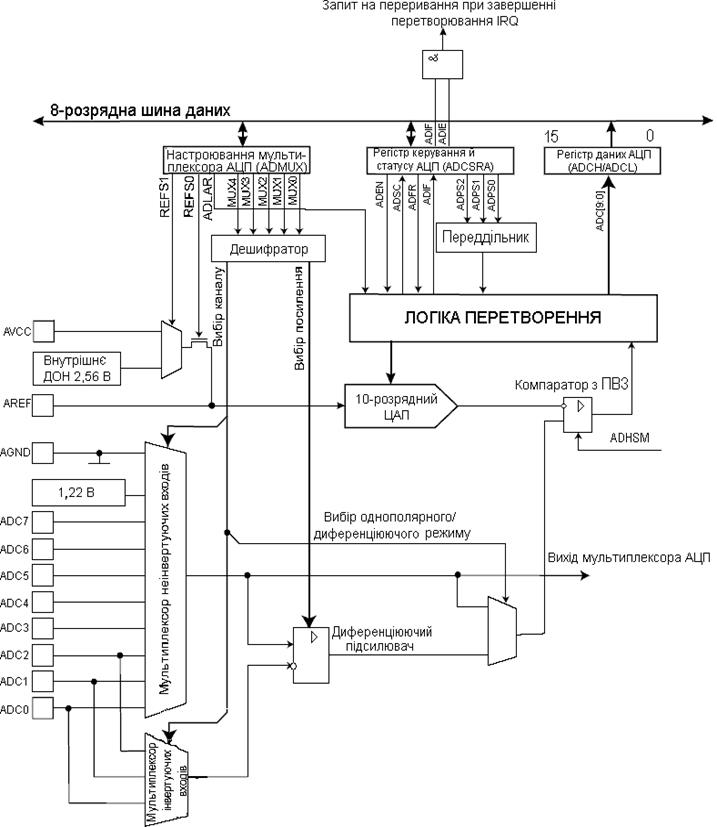

На рисунку 14 показана функціональна схема АЦП.

АЦП також підтримує введення 16 диференціальних напруг. Два диференціальних входи (ADC1, ADC0 й ADC3, ADC2) містять каскад зі ступінчастим програмувальним посиленням: 0 дБ (1x), 20 дБ (10x) або 46 дБ (200x). Для семи диференціальних аналогових каналів використовують загальний інвертуючий вхід (ADC1), а всі інші входи АЦП виконують функцію неінвертуючих входів. Якщо задано посилення 1x або 10x, то можна очікувати 8-розрядну здатність, а якщо 200x – 7-розрядну.

Рисунок 14 – Функціональна схема аналогово-цифрового перетворювача

Як внутрішня опорна напруга може бути напруга від внутрішнього ДОН на 2,56 В або напруга AVCC. Якщо потрібне використання зовнішнього ДОН, то його слід підключити до виводу AREF з приєднанням до цього виводу блокувального конденсатора для поліпшення шумових характеристик.

АЦП перетворює вхідну аналогову напругу в 10-розрядний код методом послідовних наближень. Мінімальне значення відповідає рівню GND, а максимальне – рівню AREF мінус одиницю молодшого розряду. Канал аналогового введення й каскад диференціального посилення вибираються шляхом записування бітів MUX до регістра ADMUX. Як однополярний аналоговий вхід АЦП може бути вибрано один з входів ADC0...ADC7, а також GND і вихід фіксованого джерела опорної напруги, що дорівнює 1,22 В. У режимі диференціального введення передбачено можливість вибору інвертуючих і неінвертуючих входів до диференціального підсилювача.

Робота АЦП дозволяється шляхом установлення біта ADEN в регістрі ADCSRA. Вибір опорного джерела й каналу перетворення не можна виконати до установлення ADEN. Якщо ADEN = 0, то АЦП не споживає струм, тому при переході до економічних режимів сну рекомендується спочатку відключити АЦП.

АЦП генерує 10-розрядний результат, що міститься в парі регістрів даних АЦП – ADCH й ADCL. За замовчуванням результат перетворення розміщується в молодших десяти розрядах 16-розрядного слова (вирівнювання праворуч), але може бути опціонально розташований у старших десяти розрядах (вирівнювання ліворуч) шляхом установлення біта ADLAR у регістрі ADMUX.

АЦП генерує власний запит на переривання при завершенні перетворення.

Призначення бітів регістра керування мультиплексором ADMUX

|

Номер біта |

Ім'я |

Призначення |

|

7 |

REFS1 |

Вибір джерела опорної напруги – біт 1 |

|

6 |

REFS0 |

Вибір джерела опорної напруги – біт 0 |

|

5 |

ADLAR |

Біт керування видачею результату перетворення |

|

4 |

MUX4 |

Вибір аналогового каналу й коефіцієнта підсилення – біт 4 |

|

3 |

MUX3 |

Вибір аналогового каналу й коефіцієнта підсилення – біт 3 |

|

2 |

MUX2 |

Вибір аналогового каналу й коефіцієнта підсилення – біт 2 |

|

1 |

MUX1 |

Вибір аналогового каналу й коефіцієнта підсилення – біт 1 |

|

0 |

MUX0 |

Вибір аналогового каналу й коефіцієнта підсилення – біт 0 |

Розряд 7:6 – REFS1:0. Біти вибору джерела опорної напруги. Ці біти визначають, яка напруга буде використовуватися як опорна для АЦП.

Розряд 5 – ADLAR. Біт керування показаннями результату перетворення. Біт ADLAR впливає на показання результату перетворення у двох регістрах результату перетворення АЦП. Якщо ADLAR = 1, то результат перетворення буде мати лівобічний формат, у противному випадку – правобічний.

Розряд 4:0 – MUX4:0. Біти вибору аналогового каналу й коефіцієнта підсилення. Ці біти визначають, які з наявних аналогових входів підключаються до АЦП. Крім того, з їхньою допомогою можна вибрати коефіцієнт підсилення для диференціальних каналів. Якщо значення бітів змінити в процесі перетворення, то механізм їхньої дії активізується тільки після завершення поточного перетворення (після установлення біта ADIF у регістрі ADCSRA).

Призначення бітів регістра керування й статусу АЦП – ADCSRA

|

Номер біта |

Ім'я |

Призначення |

|

7 |

ADEN |

Дозвіл на роботу АЦП |

|

6 |

ADSC |

Запуск перетворення АЦП |

|

5 |

ADFR |

Вибір режиму автоматичного перезапуску АЦП |

|

4 |

ADIF |

Прапорець переривання АЦП |

|

3 |

ADIE |

Дозвіл на переривання АЦП |

|

2 |

ADPS2 |

Керування переддільником АЦП – біт 2 |

|

1 |

ADPS1 |

Керування переддільником АЦП – біт 1 |

|

0 |

ADPS0 |

Керування переддільником АЦП – біт 0 |

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.