Розряд 7 – ADEN. Дозвіл на роботу АЦП. Запис до даного біта логічної одиниці дозволяє виконати роботу АЦП. Якщо до даного біта записати логічний нуль, то АЦП відключається, навіть якщо він перебував у процесі перетворення.

Розряд 6 – ADSC. Запуск перетворення АЦП. У режимі одиночного перетворення установлення даного біта ініціює старт кожного перетворення. У режимі автоматичного перезапуску встановленням цього біта ініціюється лише перше перетворення, а всі інші виконуються автоматично.

Розряд 5 – ADFR. Вибір режиму автоматичного перезапуску АЦП. Якщо до даного біта записати логічну одиницю, то АЦП перейде в режим автоматичного перезапуску. У цьому режимі АЦП автоматично виконує перетворення й модифікує регістри результату перетворення через фіксовані проміжки часу. Запис логічного нуля у цей біт припиняє роботу в даному режимі.

Розряд 4 – ADIF. Прапорець переривання АЦП. Даний прапорець установлюється після завершення перетворення АЦП і відновлення регістрів даних. Якщо встановлено біти ADIE й I (регістр SREG), то відбувається переривання після завершення перетворення.

Розряд 3 – ADIE. Дозвіл на переривання АЦП. Після запису логічної одиниці у цей біт за умови, що встановлено біт I у регістрі SREG, дозволяється переривання після завершення перетворення АЦП.

Розряди 2:0 – ADPS2:0. Біти керування переддільником АЦП. Дані біти визначають, на яке значення тактова частота ЦПП буде відрізнятися від частоти вхідної синхронізації АЦП.

Комбінації бітів ADPS2:0 і можливі коефіцієнти ділення наведено в таблиці 37.

Після завершення перетворення результат міститься у двох регістрах ADCL й ADCH (16-розрядний регістр ADC). Під час використання диференціального режиму перетворення результат подається в коді двійкового доповнення.

Аналоговий компаратор

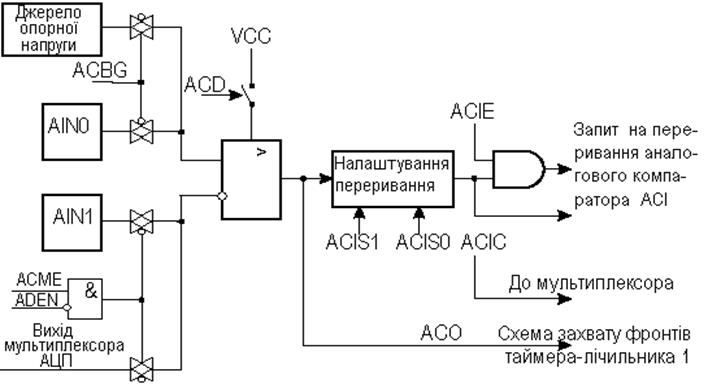

Аналоговий компаратор порівнює рівні напруг на неінвертуючому вході AIN0 і інвертуючому вході AIN1, що показано на рисунку 15. Якщо напруга на неінвертуючому вході AIN0 перевищує напругу на інвертуючому вході AIN1, то вихід аналогового компаратора ACO приймає одиничний стан. Вихід компаратора може бути настроєний для використання як джерело вхідного сигналу для схеми захвату фронтів таймера-лічильника 1. Крім того, компаратор може генерувати власний запит на оброблення переривання.

Функціональна схема аналогового компаратора зображена на рисунку 15.

Рисунок 15 – Функціональна схема аналогового компаратора

Призначення бітів регістра стану й керування аналогового компаратора ACSR

|

Номер біта |

Ім'я |

Призначення |

|

7 |

ACD |

Вимкнення аналогового компаратора |

|

6 |

ACBG |

Ввімкнення джерела опорної напруги аналогового компаратора |

|

5 |

ACO |

Вихід аналогового компаратора |

|

4 |

ACI |

Прапорець переривання аналогового компаратора |

|

3 |

ACIE |

Дозвіл на переривання аналогового компаратора |

|

2 |

ACIC |

Підключення аналогового компаратора до схеми захвату фронтів |

|

1 |

ACIS1 |

Вибір події переривання аналогового компаратора – біт 1 |

|

0 |

ACIS0 |

Вибір події переривання аналогового компаратора – біт 0 |

Розряд 7 – ACD. Вимкнення аналогового компаратора. Запис у даний розряд логічної одиниці приводить до відключення джерела живлення з аналогового компаратора.

Розряд 6 – ACBG. Підключення джерела опорної напруги до аналогового компаратора. Після встановлення даного біта до неінвертуючого входу компаратора підключається джерело опорної напруги. Після скидання даного розряду неінвертуючий вхід компаратора з'єднується з виводом AIN0 мікроконтролера.

Розряд 5 – ACO. Вихід аналогового компаратора. Даний біт виходу аналогового компаратора з’єднується безпосередньо з виходом ACO через ланцюг синхронізації.

Розряд 4 – ACI. Прапорець переривання аналогового компаратора. Даний розряд установлюється апаратно під час виникнення події відповідно до встановлення бітів ACIS1 й ACIS0. Запит на оброблення переривання аналогового компаратора виконується, якщо біти ACIE і I встановлено у регістрі SREG.

Розряд 3 – ACIE. Дозвіл на переривання аналогового компаратора. Якщо до даного розряду записано логічну одиницю й встановлено біт I у регістрі статусу, то переривання за аналоговим компаратором активізується. Запис до даного розряду логічного нуля приводить до відключення даного переривання.

Розряд 2 – ACIC. Підключення аналогового компаратора до схеми захвату фронтів. Установлення даного розряду дозволить виконати спільну роботу схеми захвату фронтів таймера-лічильника 1 й аналогового компаратора. У цьому випадку вихід аналогового компаратора підключається безпосередньо до вхідного каскаду схеми захвату фронтів, дозволяючи додати до компаратора функції заглушення шумів і настроювання фронтів переривання після захвату фронту таймером-лічильником 1.

Розряди 1, 0 – ACIS1, ACIS0. Вибір події переривання аналогового компаратора. Дані розряди визначають, яка подія приводить до процесу генерації запиту на переривання аналогового компаратора. Варіанти встановлення даних розрядів та їхнє призначення наведено у таблиці 40.

Існує можливість використовувати виводи ADC7..0 АЦП як неінвертуючі входи аналогового компаратора. Для організації такого введення застосовується мультиплексор АЦП, отже у цьому випадку АЦП слід відключити. Якщо встановлено біт дозволу на підключення мультиплексора до аналогового компаратора (біт ACME в SFIOR) і відключено АЦП (ADEN = 0 у регістрі ADCSRA), то стан розрядів MUX2..0 регістра ADMUX визначає, який вивід мікроконтролера підключено до неінвертуючого входу аналогового компаратора.

Програма

#include <avr\io.h> // Most basic include files

#include <avr\interrupt.h> // Add the necessary ones

#include <avr\signal.h> // here

int data;

void InitPorts (void);

void InitADC (void);

void InitPorts (void)

{DDRF=0x00;

}

void InitADC (void)

{ADMUX=0x49;

ADCSRA=0xec;

}

SIGNAL (SIG_ADC)

{data=ADC;

}

void main (void)

{InitPorts ();

InitADC ();

sei ();

while (1) {}

}

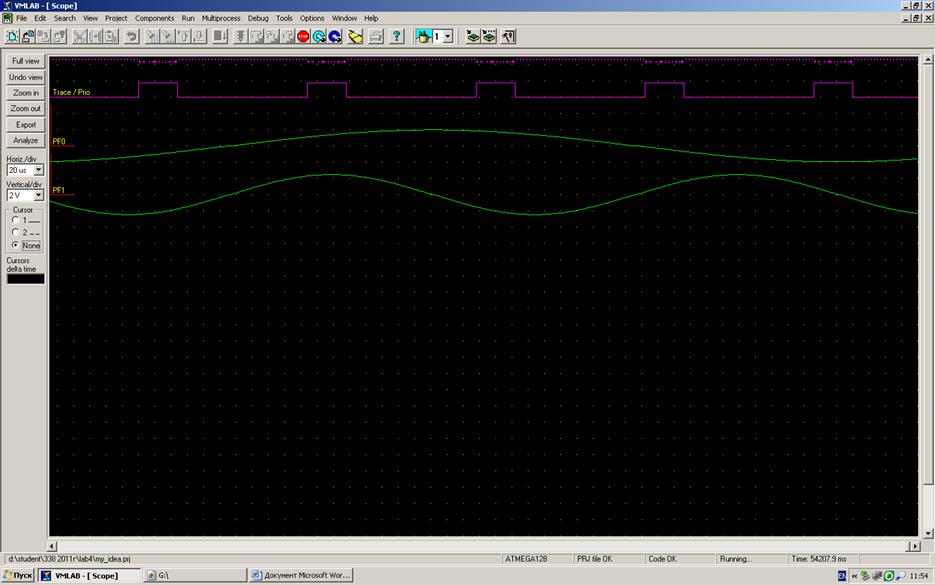

.PLOT V(PF0) V(PF1)

V1 PF0 VSS SIN(0 2 1000)

V2 PF1 VSS SIN(0 2.5 2000)

Висновок: дослідили принцип побудови, освоїли методику конфігурації й особливості застосування 10-разрядного АЦП й аналогового компаратора мікроконтролера ATmega128. Виконали завдання: подали дві напруги, що змінюються в діапазоні 2...4 В, з резистивних дільників (SLIDER) S1, S2 на входи AIN1, AIN0 компаратора. Під час збігу напруг на компараторі запускали АЦП у стартостопному режимі й перетворювали напругу, що подається на лінію 2 з дільника (SLIDER) S3 у діапазоні 1…3 В.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.