ИЛИ (например, при ошибочной установке коэффициента деления Кд>0,5 в цепи входа R), а значит, усиление сетевых наводок и импульсных помех.

Заметим к тому же, что подобранный резистором R2 (рис. 14) режим входа R критичен к изменениям и напряжения питания, и температуры. Да и вообще, наличие подбираемых элементов в цифровом устройстве, даже любительском, крайне нежелательно.

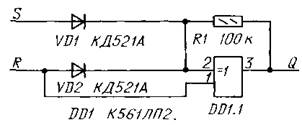

RS-триггер на элементе ИСКЛЮЧАЮЩЕЕ ИЛИ, двух диодах и резисторе. Рассмотрим схему триггера на рис. 15. В режиме хранения информации на входах триггера поддерживают низкий уровень. При этом, как уже было сказано, элемент работает повторителем, а ОС через резистор R1 положительна.

Если триггер находится в нулевом

состоянии, подача единичного импульса на вход S

переводит триггер в состо

Рис. 15'

яние 1, так как на другом входе (выв. 1) элемента продолжает действовать низкий уровень, элемент остается повторителем, а ОС — положительной.

Перед обратным переключением на верхнем по схеме входе (выв, 2) элемента высокий уровень, на входе S логическая переменная соответствует режиму хранения (8=0). При подаче единичного импульса на вход R на обоих входах элемента присутствует высокий уровень (на верхнем входе из-за действия ОС в первый момент после начала действия импульса). В результате элемент переключается и триггер переходит в нулевое состояние.

По мере уменьшения напряжения на выходе элемента открывается диод VD2, и теперь уже высокий уровень на верхнем входе поддерживается со стороны входа R триггера. Таким образом, опять на обоих входах элемента высокий уровень, что и удерживает триггер в нулевом состоянии. По окончании импульса на входе R диод VD2 закрывается, на обоих входах элемента присутствует низкий уровень (на верхнем входе из-за действия ОС). Следовательно, и после окончания импульса триггер остается в нулевом состоянии.

Таким образом, в триггере по схеме на рис. 15 резистор R1 обеспечивает положительную ОС, диод VD1 подключает вход S к элементу при установке триггера в состояние 1 и отключает его в режиме хранения, диод VD2 поддерживает примерное равенство значений напряжения на входах элемента при подаче единичного импульса на вход R и участвует в процессе переключения триггера в состояние 0.

Этот триггер не боится запрещенной комбинации, устанавливаясь в нулевое состояние, как при действии единичного импульса на входе R, т. е-вход R имеет приоритет. При неудачном выборе входов элемента в момент завершения импульса 3^1 появляется

|

|

Рис.16

"просечка" в выходном импульсе высокого уровня, но по уровню она не превышает 1/20 питающего напряжения.

Триггер, аналогичный рассмотренному, но с инверсными входами и двумя выходами Q и О, образуется при добавлении одного инвертора (рис, 16).Здесь имеет приоритет вход S. Сопротивление резистора R1 в триггерах по схеме на рис. 15 и 16 можно варьировать в пределах от 10 кОм до 1 МОм.

RS-триггер на двувыходном преобразователе уровня. Элементы микросхемы К176ПУ5 имеют прямой и инверсный выходы, что позволяет построить "полновесный" триггер (рис. 17) всего на одном таком элементе. Входные и выходные узлы элементов питают от одного источника (выв. 15 и выв. 16 соединяют вместе).

Если же по условиям работы устройства входные и выходные цепи необходимо питать от разных источников и напряжение питания на выв. 16 больше, чем на выв. 15, положительную ОС нужно подать через резистивный делитель, который уменьшит напряжение, подаваемое с выхода на вход элемента. Иначе говоря, надо добавить еще один резистор,показанный на схеме штриховыми линиями. В остальном этот триггер аналогичен тому, схема которого представлена на рис. 3,а.

Рис.17

При необходимости установления любого триггера на логических элементах в определенное состояние после включения питания следует, как указано в [1], подключить выход (выходы) триггера через резистор к плюсовому проводу питания либо к общему проводу. Пример показан на рис. 1 — этот резистор изображен штриховыми линиями.

Если триггером управляют сигналы от коммутирующих устройств или элементов с третьим состоянием, диоды из триггеров могут быть исключены (кроме триггера по схеме на рис. 6); в триггерах по схеме на рис. 14— 16 может быть исключен диод VD 1.

И наконец, нельзя обойти вниманием изящную схему (рис. 18} RS-тригге-ра на мажоритарном элементе [5]. По быстродействию, входному сопротивлению, степени развязки входов и помехозащищенности он не уступает классическому, а при_действии запрещенной комбинации R='0, S=1 не изменяет своего состояния,

В этом триггере приоритет имеет тот вход, установочный импульс на который был подан раньше, и, пока действует импульс, триггер на сигналы с другого входа совсем не реагирует. Только после окончания установочного импульса,

Рис.18

пришедшего раньше, триггер допускает управление триггером по другому входу. После снятия запрещенной комбинации триггер устанавливается в состояние, определяемое входом, с которого сигнал был снят последним.

Итак, RS-триггеры могут быть реализованы множеством способов, каждому из которых свойственны те или иные достоинства и недостатки. Об использованных в этом обзоре микросхемах и узлах на них можно прочитать в [6—8].

ЛИТЕРАТУРА

1. Осадчий В. Триггер на элементе ИСКЛЮЧАЮЩЕЕ ИЛИ, — Радио, 1989. № 9, с. 78,79,

2. Виноградов Ю. RS-триггер из логических элементов, —Радио,1995,№ 6, с-35,36.

3. Бирюков С. RS-триггер с динамическими входами. — Радио, 1996, № 6, с. 47.

4. Аваев Н. А, и др. Основы микроэлектроники. Учебное пособие для вузов. — М.:

Радио и связь, 1991, с. 123.

5. Алексеев С. Применение микросхем серии КР1533. —Радио, 1991, № 2, с. 64, 65.

6. Алексеев С. Формирователи и генераторы на микросхемах структуры КМОП. — Радио, 1985, № 8, с, 31—35.

7. Алексеев С. Применение микросхем серии К561. — Радио, 1986, № 11, с. 33—36;

№ 12, с. 42—46; 1987,№ 1,0.43—45.

8. Алексеев С. Применение микросхем серии К561. ~ Радио, 1990, Na 6, с. 54—57, 60.

Р 9/98-53

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.