Исчерпывающую информацию по системе команд процессоров х86 можно получить из следующих источников:

1. Юров В. Assembler. Специальный справочник ‑ СПб: «Питер», 2000. Книга содержит подробное описание системы команд процессоров х86.

2. Pentium Processors Family Software Developer’s Manual, vol 1: Basic Architecture. Intel, 1995. Раздел 6 содержит обзор системы команд. Документ находится на компакт-диске с материалами по курсу и доступен по гиперссылке.

3. Pentium Processors Family Software Developer’s Manual, vol 2: Instruction Set Reference. Intel, 1995. Этот документ содержит исчерпывающую справочную информацию по командам процессоров х86. Документ находится на компакт-диске с материалами по курсу и доступен по гиперссылке.

4. PentiumPro Family Developer’s Manual Volume 2: Programmer’s Reference Manual (P6VOL2.pdf,) – содержит хороший обзор системы команд по группам (Разд.6, Instruction Set Summary)

В приведенных изданиях описание команд дано «в алфавитном порядке», но содержит всю необходимую программисту информацию.

Данный обзор предназначен для того, чтобы помочь учащимся сориентироваться в огромном множестве команд процессора х86. При изложении будем следовать классификации, приведенной ранее в документе 02_2_Структура_системы_команд. В этом обзоре сделана попытка, не фиксировать внимание на специфике отдельных команд архитектуры х86, а отмечать ту их функциональность, которая имеется в любом процессоре.

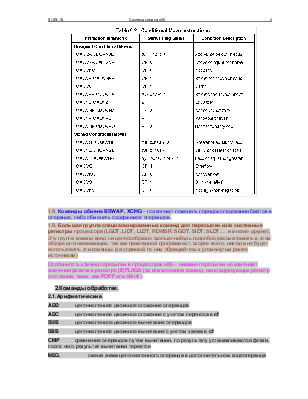

(Рисунки и таблицы заимствованы из P6VOL2.pdf, )

Семейство процессоров х86 принято относить к классу процессоров CISC (Complicated Instruction Set Computer – с усложненным набором команд). Эта совокупность свойств проявляется в нескольких аспектах:

‑ Общее количество команд в

наборе:

целочисленные ‑ 210

плавающей точки ‑ 85

ММХ ‑ 57

ММХ Pentium III ‑ 16

XMM ‑ 70

Всего: ‑ 438

‑ Базовая структура основных команд обработки – двухоперандная, один из операндов всегда располагается в регистре процессора, второй может находиться в регистре либо в памяти, причем операнд-приемник может быть как в регистре, так и в памяти.

‑ Длина команды может лежать в пределах от 1 до 15 байтов

‑ Форматы кодирования усложнены, в них исключений не меньше, чем правил

‑ Используются сложные многокомпонентные способы адресации.

‑ Структуру регистровой модели, набора команд и способов адресации нельзя назвать вполне ортогональной: многие команды, регистры в сильной степени специализированы.

‑ Команды пересылки не изменяют содержимого признаков.

Замечание: практически во всех описаниях систем команд используется термин «команды пересылки», хотя правильнее действие команд этой группы отражается словом «копирование», так как операнд-источник при выполнении действия НЕ изменяет своего значения, а в операнд-приемник помещается копия содержимого операнда-источника.

1.1.Пересылки общего назначения MOV

Позволяют пересылать (правильнее сказать – скопировать, так как содержимое источника сохраняется) операнд по схемам «регистр – регистр», «регистр – память» или «память – регистр». Имеется целый ряд ограничений на допустимые комбинации мест положений источника и приемника, в частности, нет возможности пересылки непосредственного операнда в сегментный регистр.

Не позволяют производить пересылку по схеме «память-память» (за исключением строковой (блочной) команды MOVSx).

1.2. Пересылки из/в стек: PUSH (втолкнуть в стек), POP (извлечь из стека). Используют регистр (E)SP в качестве указателя стека. Указатель стека всегда указывает на последний занятый элемент стека. Операция push sp сохраняет в стеке «старое» значение sp (в процессоре 8086 сохранялось новое значение sp).

1.3. Пересылки двоичных слов, представляющих собой адреса операндов или части (компоненты) адресов.

1.3.1. Команды загрузки «длинных адресов»: LDS, LES, LFS, LGS, LSS (Load xxx Segment)– пересылают четыре (либо два в зависимости от режима процессора) байта из памяти в регистр – указатель (в процессорах 386+ им может быть любой из регистров общего назначения), и два байта из памяти в сегментный регистр.

1.3.2. Команда загрузки исполнительного (эффективного) адреса LEA (Load Effective Address) – аналогична команде mov reg, mem, но загружает в указанный регистр reg не содержимое элемента памяти mem, а адрес этого элемента. Можно провести аналогию с операцией разадресации в Си:

iR = iB; эквивалентно mov reg, iB (присваивание)

pR = &iB эквивалентно lea reg, iB (разадресация)

1.4. Пересылки между элементами вычислительного ядра (регистры процессора, элементы памяти) и периферийными устройствами.

IN ‑ ввести содержимое из порта периферийного устройства в регистр AL или AX или EAX) OUT ‑ вывести содержимое регистра AL или AX или EAX в порт периферийного устройства, Номер порта может быть указан в команде (в пределах 0…255), либо в регистре DX.

1.5. XLAT / XLATB (transLATe Byte from table)‑ команда, позволяющая по номеру, содержащемуся в регистре AL, извлечь из таблицы байт с этим номером и переслать его в тот же регистр AL (на место номера). Начало таблицы указывается содержимым ds:[e]bx и программист его туда должен поместить заранее.

1.6. Строковые (блочные) операции.

Все

строковые команды в х86 формально не имеют операндов, но их действие

определяется значением нескольких параметров, которые должны быть занесены

предварительно в несколько регистров перед собственно строковой командой.

‑ Пара регистров ds:[e]si определяет адрес источника (1).

‑ Пара регистров es:[e]di определяет адрес приемника (2).

‑ Содержимое регистра [e]cx используется для счета обрабатываемых элементов (3).

‑ Бит (флаг) направления передачи df в регистре

состояния процессора (регистре флагов) определяет направление перебора адресов

элементов (4) при операции с цепочкой.

‑ Кроме того, мнемоника самой команды содержит указание на длину обрабатываемых

элементов строки (5).

Таким образом, строковая команда фактически использует до пяти параметров.

Для выполнения

действия с блоком элементов, перед цепочечной командой следует поставить

специальный байт – префикс повторения REPxx. При выполнении цепочечной команды пересылки с префиксом

повторения будет циклически повторяться следующая последовательность действий.

1) Элемент данных из адреса ds:[e]si пересылается по адресу es:[e]di.

2) Оба адреса после этого автоматически увеличиваются (при df=0) либо

уменьшаются (при df=1).

3) Содержимое [e]cx автоматически уменьшается на 1,

г) Если содержимое [e]cx не достигло нулевого значения, шаги а)…с)

повторяются.

Таким образом, в строковых командах фактически реализована автоиндексация (автоматическая модификация адресов при обработке элементов, расположенных в памяти подряд).

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.