MOVSB / MOVSW / MOVSD – позволяют осуществлять копирование строк (цепочек, блоков), содержащих байты, либо двухбайтовые, либо четырехбайтовые слова, из одного участка памяти в другой.

LODSB / LODSW / LODSD ‑ команды загрузки из строки в регистр al /ax /eax. Команда копирует (загружает) содержимое байта в al, либо двухбайтового слова в ax, либо четырехбайтового слова в eax. Адрес операнда-источника содержится в паре регистров ds:[e]si. После выполнения операции копирования адрес источника (содержимое регистра [e]si) увеличивается при df=0 (либо уменьшается при df=1) на длину загружаемого элемента, т.е. на 1 либо на 2 либо на 4. Команду LODS имеет смысл использовать только без префикса повторения.

STOSB / STOSW / STOSD – команды сохранения в строку из регистра al /ax /eax. Использованная с префиксом повторения, эта команда позволяет заполнить участок памяти одинаковыми элементами.

Кроме строковых пересылок в процессорах х86 имеются еще команды строковых сравнений (CMPS, SCAS и (начиная с i80286) строкового ввода-вывода.

1.7. Команды

пересылки с расширением знака –

MOVSX, MOVSZ – предназначены для выполнения операции

преобразования типа операнда одновременно с пересылкой ‑ см. в группе команд

целочисленной обработки.

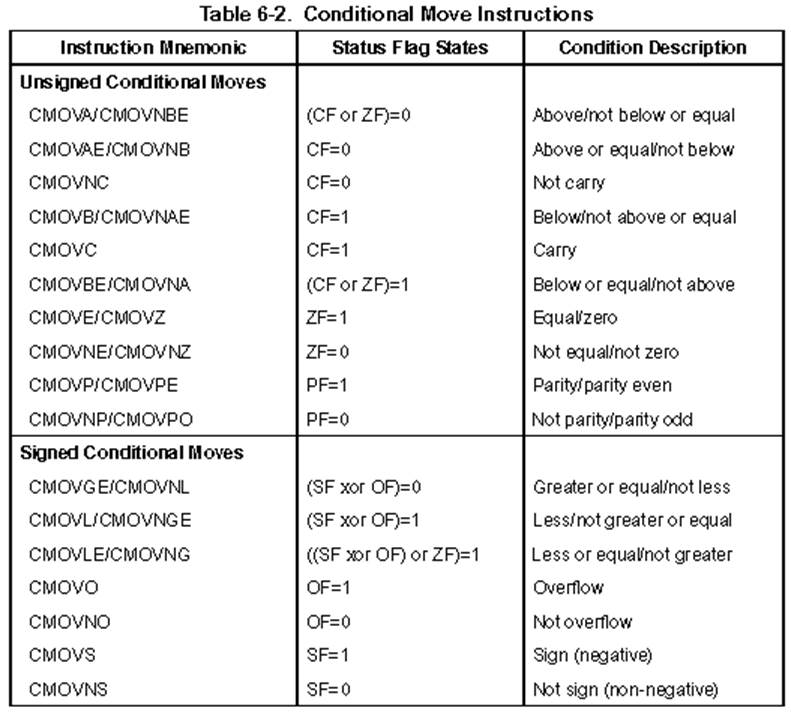

1.8. Команды условной пересылки CMOVcc – (начиная с процессоров PentiumPro) позволяют совместить в одной команде проверку условия и (не)выполнение действия – пересылка происходит только если выполнено условие, определяемое состоянием флагов. Эти команды относятся к “предикатным” командам, позволяющим реализовать условные конструкции без использования команд условного перехода, и тем самым, избежать возникновения в потоке команд “зависимостей по управлению” (Control Dependencies), заменяя их зависимостями по данным (см.напр., описание процессоров семейства IA-64, документ 24531702.pdf (Intel® IA-64 Architecture Software Developer’s Manual Volume 1: IA-64 Application Architecture)– раздел 10.

1.9. Команды обмена BSWAP, XCHG – позволяют поменять порядок следования байтов в операнде, либо обменять содержимое операндов.

1.9. Большая группа специализированных команд для пересылки из/в системные регистры процессора (LGDT, LIDT, LLDT, RDMSR, SGDT, SIDT, SLDT,… и многие другие). Эту группа команд вряд ли целесообразно сколько-нибудь подробно рассматривать в этом обзоре для начинающих, так как прикладной программист, скорее всего, никогда не будет использовать эти команды (за справкой по ним обращайтесь к упомянутым ранее источникам)

Особенность команд пересылки в процессорах х86 – никакие пересылки не изменяют значения флагов в регистре [E]FLAGS (за исключением команд, явно адресующих регистр состояний, таких, как POPF или SAHF)

2.1.Арифметические.

ADD целочисленное двоичное сложение операндов

ADC целочисленное двоичное сложение с учетом переноса в cf

SUB целочисленное двоичное вычитание операндов

SBB целочисленное двоичное вычитание с учетом заема в cf

CMP сравнение операндов путем вычитания, по результату устанавливаются флаги, после чего результат вычитания теряется

NEG, смена знака целочисленного операнда в дополнительном кодеоперанда

ASR,ASL, SAR,SAL арифметические сдвиги операнда (Arithmetic Shift to Right/Left) – эти команды эквивалентны делению/умножению на степень двойки, при сдвиге вправо знаковый бит операнда не изменяется. (См. далее описание команд сдвигов).

INC, DEC увеличение или уменьшение операнда на 1 (эти команды не влияют на флаг cf)

CBW, CWD, CDQ- расширение знака ‑ преобразование в формат с повышенной разрядностью. (Преобразование можно совместить с пересылкой, использовав команды movsx, movsz.)

MUL, DIV, IMUL, IDIV – умножение и деление беззнаковых и знаковых чисел. Разрядность операнда-приемника для произведения в командах умножения и операнда-источника для делимого в командах деления вдвое больше разрядности операндов сомножителей частного и остатка. Вследствие этого при умножении невозможно переполнение. В то же время при делении переполнение вполне возможно (при большом делимом и малом делителе).

2.2.Логические (это команды побитовой обработки)

OR - поразрядное логическое сложение. Это команда побитовой установки (т.е. записи «единицы» в заданные биты операнда).

AND - поразрядное логическое умножение. Это команда побитового сброса (записи в заданные биты «нулей»).

XOR - поразрядное исключающее ИЛИ, eXclusive OR (иногда на русском эту операцию называют «ЛИБО»). Эта двухоперандная команда фактически выполняет выборочное инвертирование битов. Например:

TEST – проверка битовых полей – команда изменяет значения флагов по результату проверки указанных битов в указанном операнде.

NOT – инвертирование операнда (замена значения каждого бита на противоположное). Это однооперандная команда.

BSF, BSR ‑ сканирование битов (поиск единичного бита в операнде-источнике, с возвратом позиции единичного бита в операде-приемнике).

BT, BTC, BTR, BTS – команды проверки значения указанного бита в операнде-источнике

Практически все команды обработки прибодят к изменению состояний (хотя бы некоторых) флагов в регистре [E]FLAGS

2.3.Сдвиги

Операция сдвига состоит в перемещении содержимого операнда в разрядной сетке. В процессорах 386+ реализовано 5 видов операции сдвигов, которые различаются тем, что происходит с битами, выходящими за пределы разрядной сетки с одного «конца» операнда, и с освобождающимися позициями на другом его «конце». Количество сдвигов для каждого из видов может быть либо равно 1, либо задается содержимым регистра cl, либо непосредственной константой в команде. Таким образом, любая команда сдвига (за исключением shld и shrd) имеет два параметра: что сдвигать, и на сколько позиций.

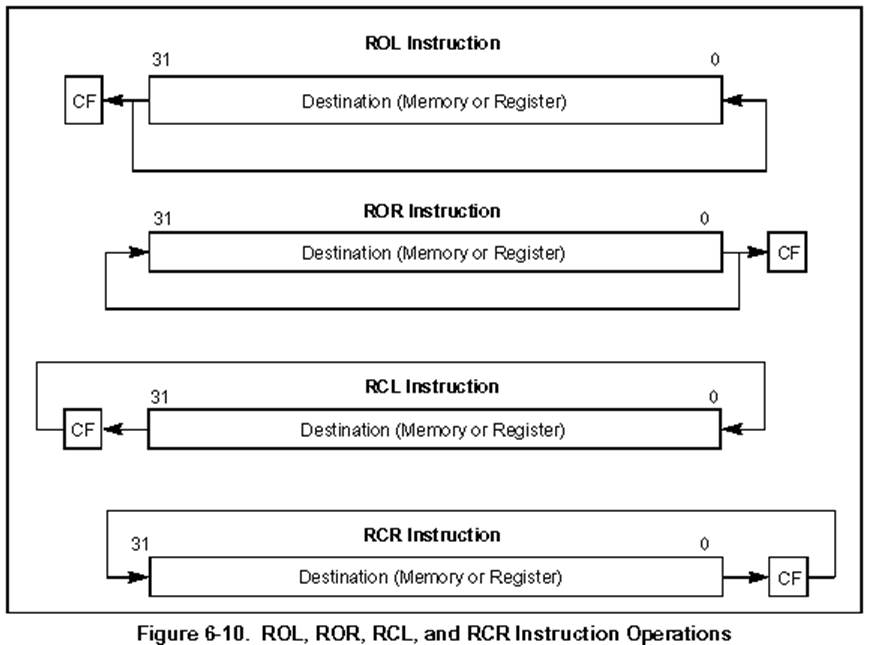

1) ROR, ROL, RCR, RCL –циклические сдвиги (мнемоника образована от слова rotate – вращать). При циклическом сдвиге то, что выходит за границу разрядной сетки операнда, помещается в освобождающуюся позицию на другом конце операнда. В процессорах х86 существует две разновидности циклических сдвигов: во второй разновидности «вращение» операнда происходит с участием флага cf.

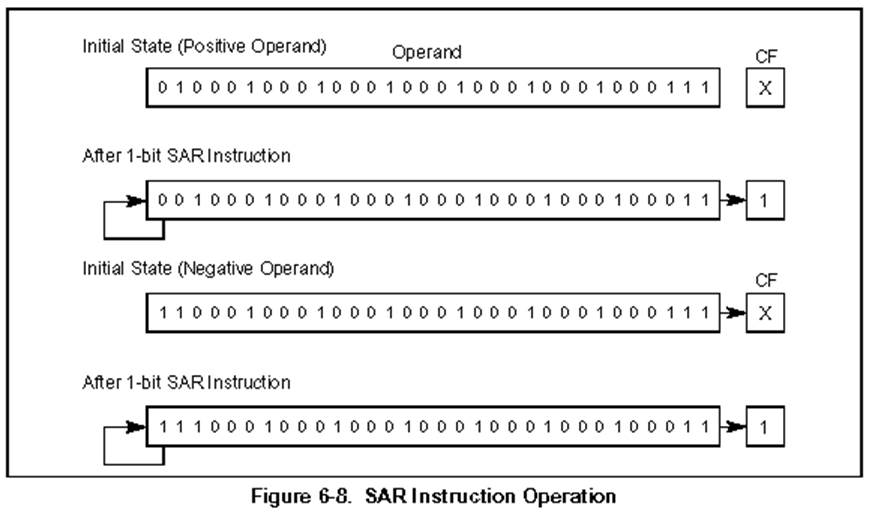

2) SAR,SAL - арифметические сдвиги (мнемоники – от слов shift arithmetic). Эта разновидность сдвига осуществляется таким образом, что результат оказывается эквивалентен умножению (при сдвиге влево) или делению (при сдвиге вправо) операнда на основание системы счисления, т.е. на 2. Для этого, при сдвиге вправо, старший (знаковый) разряд операнда сохраняет свое первоначальное значение. См. двоичное представление чисел со знаком.

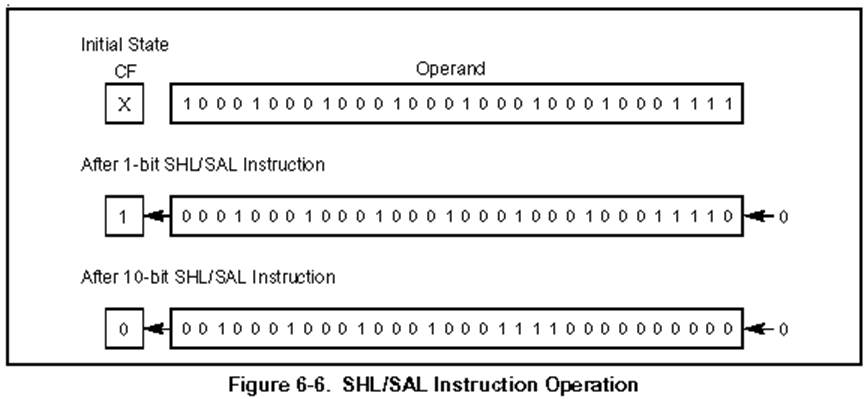

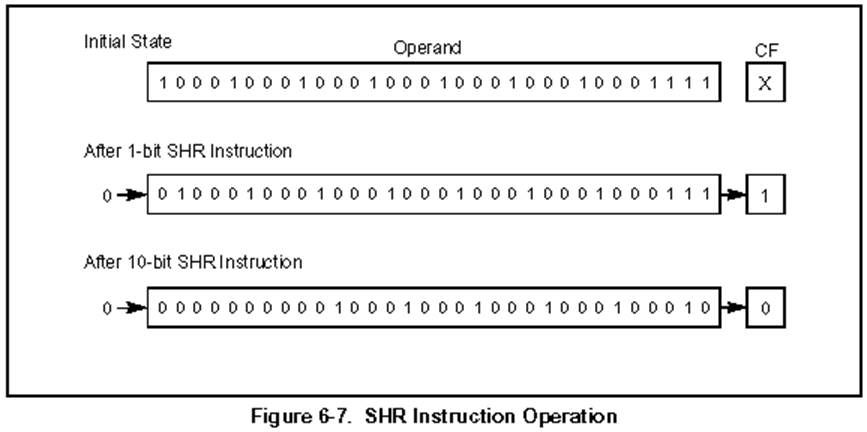

3) SHL,SHR - логические сдвиги. При выполнении логических сдвигов биты, «выдвигаемые» из разрядной сетки, теряются, а противоположный конец операнда заполняется «нулями».

(Заимствовано из P6VOL2.pdf, стр. 6-22 или 104 …105 по сквозной нумерации)

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.