Перелік елементів.

Всі відомості про елементи, які входять у склад пристрою і зображені на схемі, записують у перелік елементів, який оформляють у вигляді таблиці. Таблицю розміщують на листі схеми електричної принципової, за формою (рис.6)

|

Рис.6. |

В таблицях (Додаток )повинна бути вказана наступна обов'язкова інформація:

- Позиційне позначення мікросхем;

- Найменування IС;

- Номер виводів живлення і загальний.

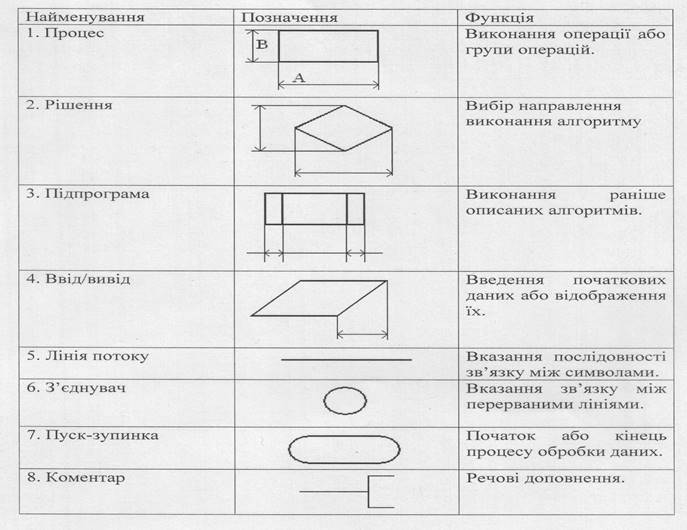

Правила виконання схем алгоритмів і програм

В процесі виконання роботи необхідно розробити схему алгоритма функціонування пристроїв за допомогою умовно-графічних позначень - символів за ДСТУ 19.003-91 .

УГП відображає основні операції процесу обробки даних, програмування і зв'язані один з одним за допомогою ліній потоку. В середині символа чи разом з ним можуть бути розміщені записи і позначення для уточнення виконуємих ними функцій.

Пояснення щодо використання елементів схеми електричної принципової.

Рекомендована спрощена структурна схема проектуємої системи зображена на рис.1. В курсовій роботі необхідно зобразити більш детальну структуру системи взявши за основу схему приведену на рис. 1. Обов'язково зобразити всі шинні з'єднання відповідно їх позначивши, найменування основних ліній керування процесором та контролером.

Рис. 1 Структурна схема

Організація МПС

1.1 Блок центрального процесора.

Головним елементом блоку центрального процесора (БЦП) є мікропроцесор КР580ВМ80А. Цей мікропроцесор являє собою 8-розрядний процесор, у якому сполучені операційні й керуючі пристрої. Керуюча пам'ять недоступна користувачеві, у ній уже в процесі виготовлення ВІС записуються мікропрограми операцій. Таким чином, передбачається використання деякої фіксованої системи команд, у яку користувач не може внести змін. У зв'язку із цим даний мікропроцесор ставиться до числа немікропрограмуємих.

Виконання кожної команди виробляється мікропроцесором у строго певній послідовності дій, що визначається кодом команди й синхронізується сигналами Ф1 і Ф2 тактові генератори. Цикл команди – це час виконання команди. За цей час: команда вибирається з пам'яті, дешифрується код команди, формуються керуючі сигнали для виконання команди, завершується вплив керуючих сигналів. Цикл команди розбивається на машинні цикли – це час, необхідний для звертання до пам'яті або до пристроїв вводу - виводу.

Цикл команди складається зі скількох машинних циклів, скільки звертань до пам'яті або до ПВВ буде потрібно для виконання цієї команди. Команди цього мікропроцесора можуть містити від 1 до 5 машинних циклів.

У свою чергу кожен машинний цикл складається з тактів – найменший проміжок часу, необхідний для виконання однієї елементарної дії в мікропроцесорі. Такт дорівнює 1 періоду тактових імпульсів тактового генератора. Машинний цикл може складатися від 3 до 5 тактів. Перші три такти потрібні для організації обміну з пам'яттю, а другий і третій такти - для виконання внутрішніх операцій у мікропроцесорі. Відлік тактів ведеться від позитивних фронтів імпульсної послідовності Ф1. При виконанні будь-якої команди спочатку зчитується перший байт команди з пам'яті. Прості команди виконуються за один машинний цикл; складні команди - за 5 машинних циклів з вісімнадцятьма тактами.

Для формування керуючих сигналів штучно мультиплексують шину даних, тобто на початку кожного машинного циклу на шину даних мікропроцесор виставляє 8 керуючих сигналів, називаних байтом стану. Байт стану вказує, який з машинних циклів виконується в даний момент, тобто до якого із зовнішніх пристроїв відбувається обіг. Байт стану виставляється на шину даних по передньому фронті сигналу Ф2 у першому такті й знімається із шини даних по передньому фронті Ф2 у другому такті. Для того, щоб показати, що йде процес передачі байта стану, використається вихід SYNC мікропроцесора: при виводі байта стану на виході SYNC =1. Сигнал SYNC=1 дозволяє виділити байт стану з інформації переданої по шині даних. Байт стану видається на шину даних в інтервалі SYNC=1, а використається протягом усього машинного циклу. Тому байт стану запам'ятовується в спеціальному регістрі слова-стану. Запис виробляється з використанням сигналів SYNC =1 і Ф2=1. Дешифратор перетворить байт стану необхідні для поточного машинного циклу системні керуючі сигнали. При формуванні цих керуючих сигналів для узгодження блоків МПС по тимчасових характеристиках використаються вихідні сигнали мікропроцесора DBIN й WR. Регістр слова-стану й дешифратор, що забезпечують формування системних керуючих сигналів, називаються системним контролером.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.