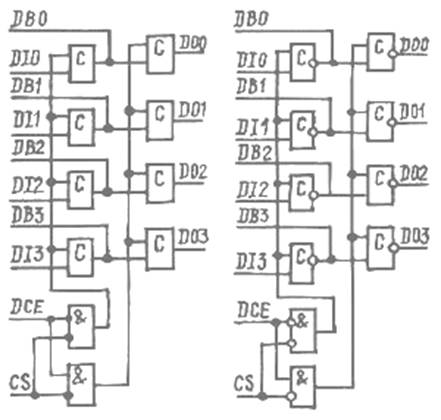

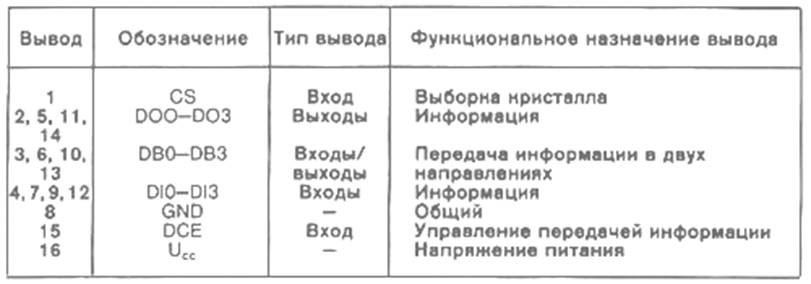

Мікросхеми К589АП16 і К589АП26 - двунаправленние шинні формірователі, свого роду підсилювачі цифрових сигналів. Відрізняються вони тим, що, проходячи через мікросхему К589АП16, сигнал залишається незмінним, а через К589АП26 - інвертується. Використовуються ці мікросхеми для керування шинами (магістралями) в цифрової та мікропроцесорної техніки. Обидві мікросхеми представляють собою 4-канальні комутатори, що мають у кожному каналі одну шину тільки для прийому інформації та одну двунаправленную шину для прийому та видачі інформації. Умовне графічне позначення мікросхем показано на малюнку 11, а структурна схема - на малюнку 12. Призначення висновків зазначено в таблиці 7.

Для керування режимами роботи та напрямком видачі інформації використовується спеціальна схема на двох елементах 2І. При появі на вході CS подається логічна 1, формірователі переходять у вимкненому високоомное стан. При наявності на вході CS логічного 0 управління видачею інформації по шинам D0 та DВ здійснюється сигналом на вході управління видачею інформації DСЕ. Якщо на вході DCE логічний 0, то відкрита передача інформації з входів DI на виходи DВ. При сигнал з рівнем логічної 1 на цьому ж вході відбувається передача інформації з входів DВ на виходи 0 (див. таблицю 8).

Шинний формірователь і шинний формірователь з інверсіей типів К589АП16 і К589АП26 відповідно являють собою четирехканальние комутатори і призначені для збільшення нагрузочной здібності МОП ВІС при підключенні їх до системної магістралі. Виходи ШФ і ШФІ мають три стану. У ШФІ вхідні сигнали інвертуються. Корпуса обох схем 16-вивідні. К589АП16, виконують потрійну роль:

-підсилюють сигнали по потужності, зняті з висновків DO-D7MH

-відключають висновки В1-В4 від загальної шини, коли на ВК надходить сигнал ПЗХ;

-двунаправленную забезпечують передачу даних при Чтеніі і запису.

|

|

||

|

Рис. 10. Графическое обозначение м/сх К589АП16 и К589АП26 |

Рис. 11 Структурная схема м/сх К589АП16 и К589АП26

Табл.10

|

Таблица 11

|

4.Розробка структурної схеми

Відповідно до завдання враховується, що внутрішньо системна магістраль сформована, а у якості пристрою обміну інформацією слід використовувати ВІС програмованого паралельного інтерфейсу КР580ВВ55А. Для організації двостороннього обміну між системною магістраллю та ВІС, між ВІС та об’єктом, а також для забезпечення погодження роботи мікросхем по струму використовуємо магістральні прийомопередавачі з трьома етапами на виході, у якості яких обираємо мікросхеми КР580ВА86 та КР580ВА87. Ці мікросхеми я обрав тому, що у мене в завданні усі режими 0, тобто просте введення/виведення і немає стробів. Мікросхеми К589АП16 і К589АП26 призначені для формування стробів. Мікросхеми КР580ВК28 і КР580ВК38 призначені для формування сигналів І/OW, MEMW відносно сигналів WR „ Запис” та STSTB „Строб стану” відповідно. Мікросхеми КР580ВА86/87 більш придатні для практичного використання у порівнянні з мікросхемами К589АП16/26,тому що достатні для буферування усієї 8-розрядної шини даних.

Інформація від об’єкта повинна вводитися через порти РА, необхідно виходи приймачів А мікросхеми КР580ВА86 з’єднати з портами РА, а входи приймачів В – до об’єкту. Інформація до об’єкту повинна виводитися через порти РВ, РС1, РС2, необхідно входи приймачів А мікросхеми КР580ВА86 з’єднати до портів РВ, РС1, РС2, а виходи приймачів В з’єднати з об’єктом.

ВІС паралельного інтерфейсу працює в режимі 0. Для організації двостороннього обміну даними між шиною даних ( ШД ) та портом необхідно використовувати додатковий шинний формувач ШФDB. Режим роботи формувача на приймання чи передачу даних визначається сигналом Чт В/В, який повинен взаємодіяти тільки при виборі модуля відповідної адресою. Вибір модуля відповідною адресою повинен здійснюватись за допомогою дешифратора ДА коду на адресних шинах А2-А7, а вибір відповідного порту його регістра за допомогою адрес А0, А1. Вочевидь, що для запису інформації в порт і її зчитування ДА повинен регулюватися сигналами Чт В/В, Зп В/В.

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.