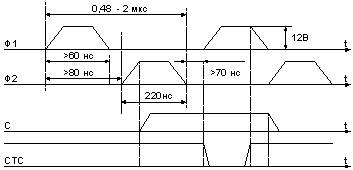

ІС ГТВ містить генератор Г гармонійних коливань, до висновків К1 і К2 якого підключається кварцовий резонатор. Гармоніческіе коливання з виходу генератора надходять на вихід ІС ГТВ і використовуються всередині нього для управління схемами формування тактірующіх послідовностей Ф1 і Ф2, сигналу скидання СБ і сигналу готовності ГТ. Наявність гармонійних коливань на виведенні ОСЦ ГТВ може бути використана для контролю за його роботи або у зовнішніх модулях МС. Висновок Ф2Т ГТВ використовується для виведення з генератора сигналу високого рівня стандартного для ТТЛ-схем, тривалістю п'ять періодів опорної частоти кварцового резонатора. Цей сигнал може бути використаний у зовнішніх пристроях як еталонний імпульсний сигнал стабілізваной частоти. Вивід СБ.в використовується для підключення кнопки КН, що переводить МП в ре жім початкової установки. Зауважимо, що формування системного стробірующего сигналу СТС здійснюється ІС ГТВ після подачі на його висновок СВ (вхід сінхросігнала) сінхросігнала С з відповідного висновку МП.Временние співвідношення тактових імпульсних послідовностей Ф1 і Ф2 і формування системного сигналу СТС показані на рис. 3.

Рис.3

Рис.3

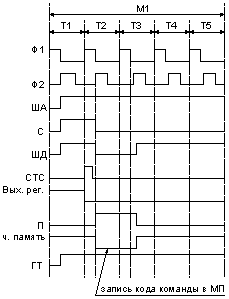

За переднього фронту тактірующего сигналу Ф2 сінхросігнал З подається на вхід СВ ГТВ і з його допомогою на висновок СТС ГТВ пере дається інвертірованний сигнал Ф1, який є системним стробом СТС.Процесс виконання будь-якої команди мікропроцесора розбивається на цікли.обозначаемиеМ1, М2 ,..., М10. У кожному циклі відбувається одне звернення мікропроцесора до пам'яті або зовнішнього пристрою (ВУ). Кожен цикл розбивається на такти Т1, Т2, ..., Т5. Самий тривалий цикл виконання команди становить 5 тактів. У мікропроцесорі КР580ВМ80А можуть виконуватися наступні машинні цикли: М1, що розташовуються - вибірка коду операції, М2 –зчитування з пам'яті, МОЗ - запис в пам'ять, М4 - зчитування з стека, М5 - запис у стек, Мб - введення інформації, М7 - висновок інформації, М8 - підтвердження переривання, М9 - підтвердження зупину, М10 - підтвердження переривання при остановці.Роздивимось послідовність виконання першого циклу будь-якої команди циклу М1 вибірки коду операції. Як відомо, коди всіх команд знаходяться в комірках пам'яті. Тому в першому такте Т1 з переднього фронту сигналу Ф2 на ША лічильник команд PC виставляє адреса комірки пам'яті, в якій міститься чергова команда, що підлягає виконанню (рис. 4).

Рис. 4

Рис. 4

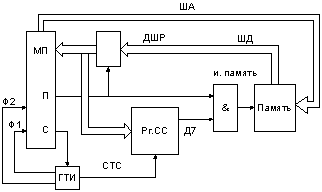

При цьому схема збільшення мікропроцесора автоматично збільшує на одиницю вміст лічильника PC. Одночасно з появою адреси на ША, МП виробляє сінхросігнал С, а на шину даних ШД видає байт слова стану, значення розрядів якого (табл.4) використовуються далі для формування керуючих сигналів, що діють в протягом усього поточного циклу. Для збереження на час виконання циклу «слово стану» записується в регістр-засувку. Здійснюється це в такий спосіб (рис.5).

Рис. 5

Таблица 4

|

Разряд |

Обозначение |

Назначение |

|

DO |

INTA |

Сигнал подтверждения прерывания. Используется для разрешения вы¬дачи на ШД первой команды после прерывания при активном сигнале «П» |

|

D1 |

WO (ЗП) |

Указывает, что операция в текущем цикле цикле является операцией записи (при WO = 0) или чтения (при WO = 1) |

|

D2 |

STACK (CTK) |

Означает наличие на шине адреса содержимого указателя стека |

|

D3 |

HLTA |

Сигнал подтверждения команды остановка |

|

D4 |

OUT (ОСТ) |

Указывает, что в текущем цикле вы¬полняется операция вывода |

|

D5 |

M1 |

Указывает, что текущий цикл служит для выборки первого байта команды |

|

D6 |

INP (ВЫВ) |

Указывает, что в текущем цикле выполняется операция ввода |

|

D7 |

MEMR (ЧТП) |

Указывает, что в текущем цикле производится чтение памяти |

Уважаемый посетитель!

Чтобы распечатать файл, скачайте его (в формате Word).

Ссылка на скачивание - внизу страницы.